# 博士論文

メモリスロット装着型ネットワークインタフェースにおける 低遅延通信機構に関する研究

2007年度

慶應義塾大学大学院理工学研究科

辻 聡

### 論文要旨

近年, 汎用のパーソナルコンピュータ (PC) を多数, 相互に接続した PC クラスタが高性能計算機の主流となっている. PC クラスタにおいて, PC 間のインターコネクトにはGigabit Ethernet のような汎用的なネットワークのほか, Myrinet や QsNET, InfiniBandといった専用のネットワークが用いられる.

こういったインターコネクトのネットワークインタフェースは PC の汎用 I/O バスに装着されるが、長い間 32bit/33MHz の PCI バスが PC における汎用 I/O バスのデファクトスタンダードであった。32bit/33MHz PCI バスの最大スループットは 132MByte/sと、インターコネクトのスループットが数百 MByte/s に達していたことを考えると非常に低い値であった。サーバやワークステーションには 64bit 幅の PCI バスや PCI バスの上位規格である PCI-X バスが搭載されており、I/O バスの性能は高かった。しかし、PC に比べると高コストであるため、これらを用いて PC クラスタを構築すると PC クラスタの利点の 1 つであるコストパフォーマンスの高さが損なわれてしまう。

一方、PC に搭載されているメモリバスはホストプロセッサの性能向上に追随する必要があることから、汎用 I/O バスよりもスループット、アクセスレイテンシの面で性能が高く、また、性能向上率も良いという利点がある。このことから、メモリスロットに装着するネットワークインタフェースである MEMOnet が 1999 年に提案された。本研究では DIMM スロットに装着する MEMOnet である DIMMnet を用いて、低レイテンシかつ高スループットな通信を実現することを目的とする.

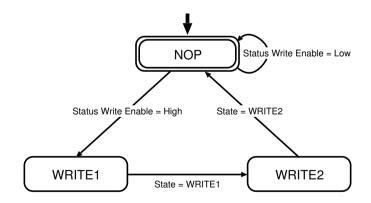

本研究で用いた DIMMnet は第二世代目の DIMMnet-2 である. DIMMnet-2 は PC の DDR-SDRAM スロットに装着する. 本研究ではコントローラに Xilinx 社の FPGA で ある Virtex-II Pro を搭載した試作基板を対象に、ネットワークインタフェースコントローラの設計、及び実装を行い、基本通信性能の評価を行った. 試作基板には FPGA の ほかに 2 枚の DDR SO-DIMM や IEEE 10GBASE-CX4 コネクタが搭載されており、このコネクタと FPGA 内蔵の高速シリアルトランシーバを用いることで、InfiniBand (4X: 10Gbps) のネットワークに接続することを可能にしている.

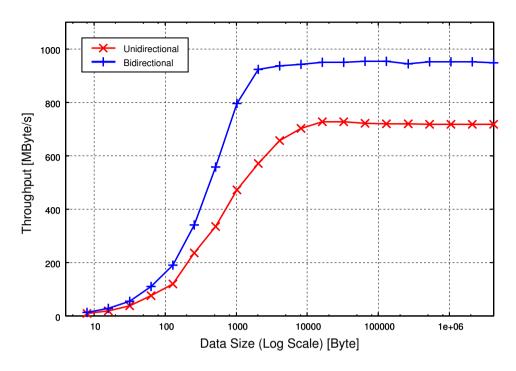

本実装では通信処理やメモリアクセスなどの DIMMnet-2 で実行されるすべての処理をハードワイヤードで実現し、ソフトウェアによる処理を介在させないことで通信性能の向上を達成している。 DIMMnet-2 に搭載した低遅延通信機構である BOTF (Block On-The-Fly) の評価の結果、片方向の最小の通信遅延が  $0.632\mu s$  であった。 また、BOTF は PIO (Programmed I/O) による通信ながら、BOTF を連続して実行することで、片方向で 631.11MByte/s,双方向で 1163.70MByte/s という高いスループットを達成した。 これらの値は冒頭で述べた PC クラスタ専用のインターコネクトに匹敵する性能である。 これらの評価を通し、メモリスロットを利用することで低コストな汎用 PC においても高い通信性能を得られることを示した。

さらに、MPI (Message Passing Interface) に代表されるメッセージ通信を支援するためのメッセージ "受信"機構である IPUSH (Indirect PUSH) や LHS (Limited-length Head Separation) の提案,及び実装を行った。これらの受信機構の評価を行い、メッセージ通信時における受信バッファの利用の効率化やメッセージタグの比較のオーバヘッドが削減可能であることを示した。これらは汎用 I/O バスに装着する一般的なインターコネクトに対しても適用可能であり、メッセージ通信を用いるシステムにおいて性能向上が期待できる。

### **Abstract**

Recently, a PC (Personal Computer) cluster, which is consisting of many PCs connected each other with networks, has been a mainstream of high performance computing in most of enterprises and laboratories. For networks in such PC clusters, Myrinet, QsNET and InfiniBand as dedicated networks are used as well as Gigabit Ethernet. The network interfaces for such networks are attached into general I/O buses on PCs. However, the de-fact standard I/O bus; PCI bus running at 33 MHz with 32-bits data width supported only 132 MByte/s throughput, and it was far less than that of the networks. On servers and high-end workstations, high performance I/O buses; PCI bus with 64-bits data width and PCI-X bus were equipped. However, their expensive cost often spoiled the high degree of performance per cost, which is the fundamental benefit of PC clusters.

In contrast, the performance of memory system is higher than that of general I/O buses in order to adapt to the improvement trend of host processors. MEMOnet, a network interface attached into memory slot, was proposed in 1999 to make the best use of this performance. One of the forms of MEMOnet attached into DIMM slot is called DIMMnet.

This research is about designing a network controller logic for DIMMnet-2 which is the second generation of DIMMnet attached into the DDR-SDRAM memory slot, and supports the low latency and high throughput communication. The DIMMnet-2 prototype board used for implementation of the network controller has an FPGA (Virtex-II Pro) with a high speed serial transceiver, two DDR SO-DIMMs and an IEEE 10GBASE-CX4 connector. DIMMnet-2 is connected to InfiniBand network (4X: 10Gbps) using the transceiver and the connector.

All primitive operations on DIMMnet-2 have been implemented with hard-wired logic in the FPGA to improve the communication performance. The performance at micro-benchmark level has been evaluated on the controller. The results indicate that the lowest unidirectional latency of BOTF (Block On-The-Fly) communication mechanism is  $0.632 \,\mu s$ . Although the BOTF is for short messages using PIO (Programmed I/O), the throughput is reached at 631.11 MByte/s with unidirectional communication and 1163.70 MByte/s with bidirectional by issuing multiple BOTF requests continuously. They are even equal to those of other recent high performance networks. Thus, it is shown that the general PCs are able to get high communication performance by utilizing the memory slot.

Moreover, the message-receiving mechanisms, IPUSH (Indirect PUSH) and LHS (Limited-length Head Separation), are proposed and have been implemented. These mechanisms support the processing of message passing like MPI (Message Passing Interface). In the result of the evaluation, the efficiency of memory usage and the improvement of the overhead of comparing message tags are showed. These mechanisms are able to be applied to other networks attached into general I/O buses, and the performance improvement is expected on the parallel distributed computing systems using message passing.

# 目次

| 第1章 | 緒論                                         | 1  |

|-----|--------------------------------------------|----|

| 1.1 | DIMMnet-2 プロジェクト                           | 3  |

| 1.2 | DIMMnet-2 プロジェクトにおける筆者の貢献                  | 3  |

| 1.3 | 本論文の構成                                     | 4  |

| 第2章 | 関連研究                                       | 6  |

| 2.1 | メモリスロットを機能拡張に用いるシステム                       |    |

|     | 2.1.1 MINI                                 | 6  |

|     | 2.1.2 Pilchard                             |    |

|     | 2.1.3 TKDM                                 | 8  |

|     | 2.1.4 DIVA PIM                             | 8  |

|     | 2.1.5 まとめ                                  | 9  |

| 2.2 | 並列分散処理環境用インターコネクト                          |    |

|     | 2.2.1 RHiNET                               | 11 |

|     | 2.2.2 Myrinet                              | 15 |

|     | 2.2.3 Quadrics Network                     | 17 |

|     | 2.2.4 InfiniBand                           | 20 |

|     | 2.2.5 10Gigabit Ethernet                   | 23 |

|     | 2.2.6 まとめ                                  | 24 |

| 2.3 | メッセージ通信を支援する通信機構                           | 25 |

|     | 2.3.1 受信側がメッセージの受信先アドレスを指定する受信機構           | 26 |

|     | 2.3.2 ネットワークインタフェースコントローラによる MPI のメッセージ受信処 |    |

|     | 理の高速化                                      | 27 |

|     | 2.3.3 まとめ                                  | 28 |

| 第3章 | DIMMnet                                    | 31 |

| 3.1 | DIMMnet-1                                  | 31 |

|     | 3.1.1 DIMMnet-1 の問題点                       | 32 |

| 3.2 | DIMMnet-2                                  | 33 |

|     | 3.2.1 DIMMnet-2 試作基板                       | 35 |

| 3.3 | メモリスロットにネットワークインタフェースを装着することによる問題点         | 38 |

|     | 3.3.1 PC に搭載可能な主記憶の最大容量の問題                 | 38 |

|     | 3.3.2 Dual Channel 動作への対応の問題               | 38 |

| 3.4 | 本研究の目的                                     | 39 |

| 第4章 | DIMMnet-2 ネットワークインタフェースコントローラの設計               | 40 |

|-----|------------------------------------------------|----|

| 4.1 | DIMMnet-2 ネットワークインタフェースコントローラの概要               | 40 |

| 4.2 | Core Logic の設計                                 | 42 |

|     | 4.2.1 Core Logic ホストインタフェース部                   | 43 |

|     | 4.2.2 Core Logic 要求処理部                         | 45 |

| 4.3 | DIMMnet-2 におけるデータ転送                            | 46 |

| 4.4 | DIMMnet-2 におけるプロセスの識別                          | 46 |

|     | 4.4.1 プロセス識別子の管理                               | 48 |

| 4.5 | Core Logic ホストインタフェース部のメモリ領域                   | 49 |

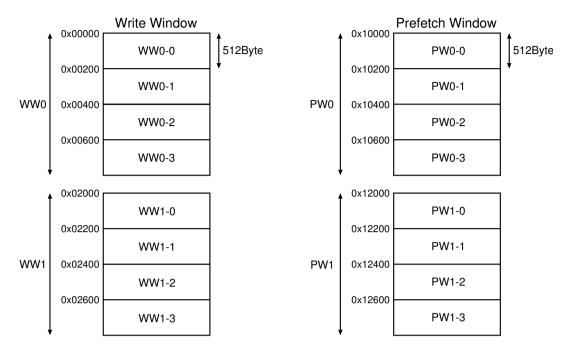

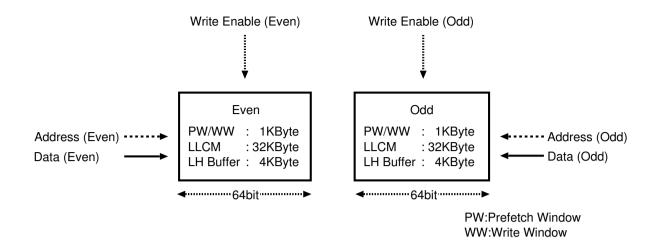

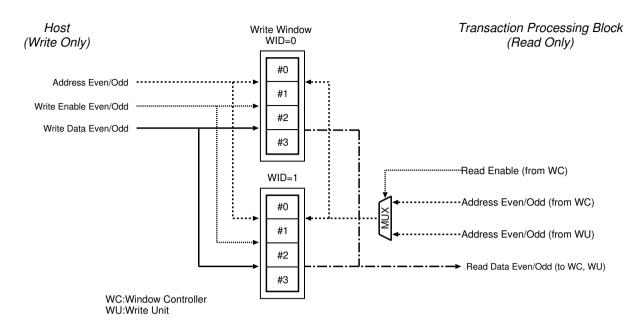

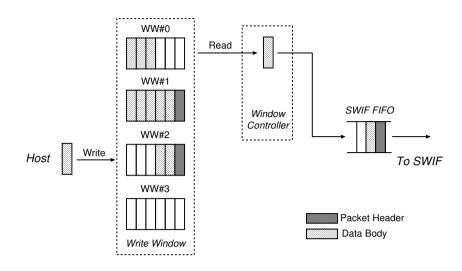

|     | 4.5.1 Write Window                             | 49 |

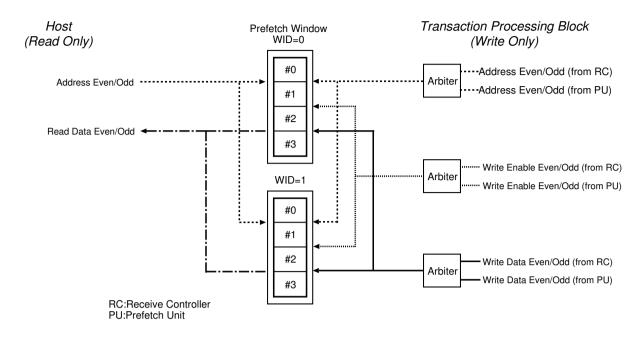

|     | 4.5.2 Prefetch Window                          | 50 |

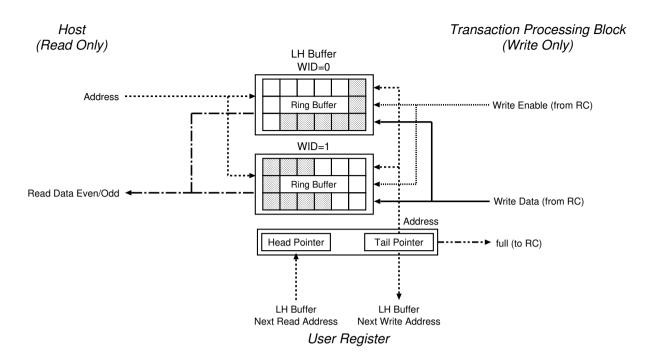

|     | 4.5.3 LLCM                                     | 50 |

|     | 4.5.4 LH Buffer                                | 50 |

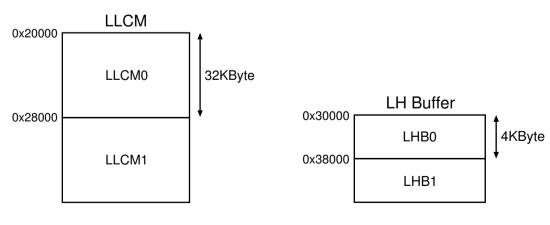

|     | 4.5.5 User Register                            | 51 |

|     | 4.5.6 System Register                          | 58 |

| 4.6 | プリミティブ                                         | 60 |

|     | 4.6.1 NOP (No OPeration)                       | 60 |

|     | 4.6.2 BOTF (Block On-The-Fly)                  | 61 |

|     | 4.6.3 VL 系列 (Vector Load Family)               | 61 |

|     | 4.6.4 VS 系列 (Vector Store Faimily)             | 62 |

|     | 4.6.5 RVL 系列 (Remote Vector Load Family)       | 64 |

|     | 4.6.6 RVS 系列 (Remote Vector Store Family)      | 65 |

|     | 4.6.7 IPUSH 系列 (Indirect PUSH Family)          | 65 |

|     | 4.6.8 SO-DIMM 間コピー                             | 65 |

|     | 4.6.9 Command Ex を利用した拡張プリミティブ                 | 66 |

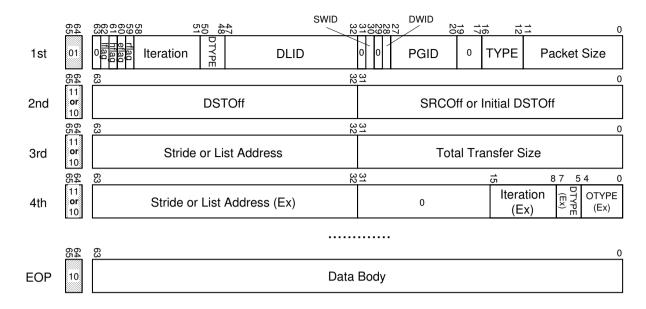

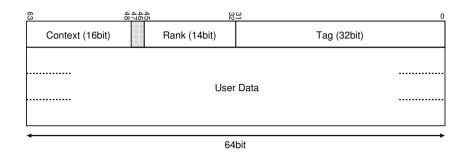

| 4.7 | パケットフォーマット                                     | 66 |

|     |                                                |    |

| 第5章 | 実装                                             | 69 |

| 5.1 | Write Window, Prefetch Window, LLCM, LH Buffer |    |

|     | 5.1.1 Write Window                             |    |

|     | 5.1.2 Prefetch Window                          | 69 |

|     | 5.1.3 LLCM                                     | 70 |

|     |                                                | 70 |

| 5.2 |                                                | 71 |

|     |                                                | 71 |

|     |                                                | 72 |

| 5.3 |                                                | 74 |

|     | 5.3.1 Request Acceptor                         | 75 |

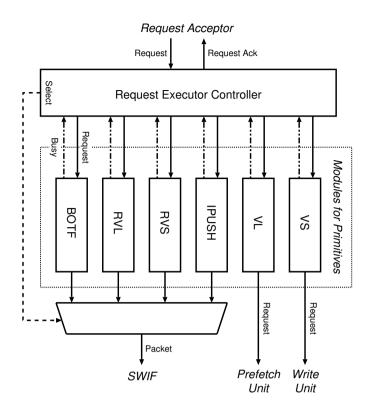

|     | 5.3.2 Request Executor                         | 76 |

|     |                                                | 77 |

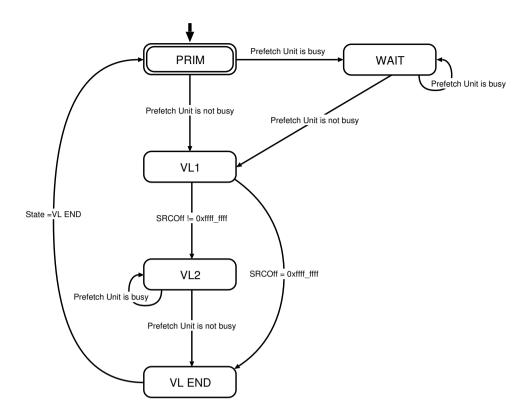

|     | 5.3.4 VL 系プリミティブ処理時の状態遷移                       | 79 |

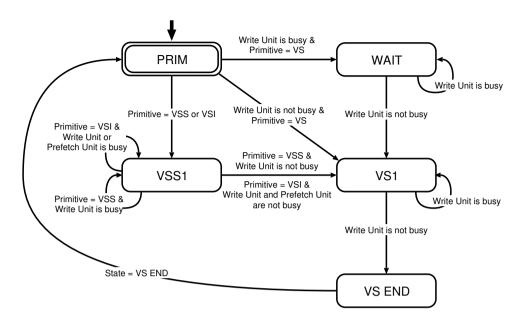

|     | 5.3.5 VS 系プリミティブ処理時の状態遷移                       |    |

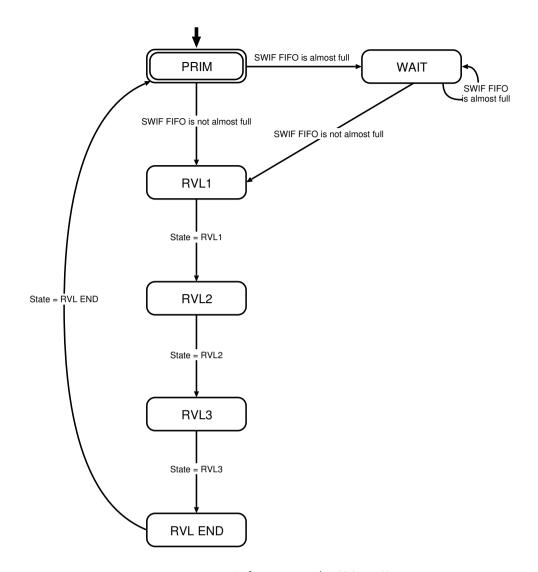

|     | 5.3.6 RVL 系プリミティブ処理時の状態遷移                      | 82 |

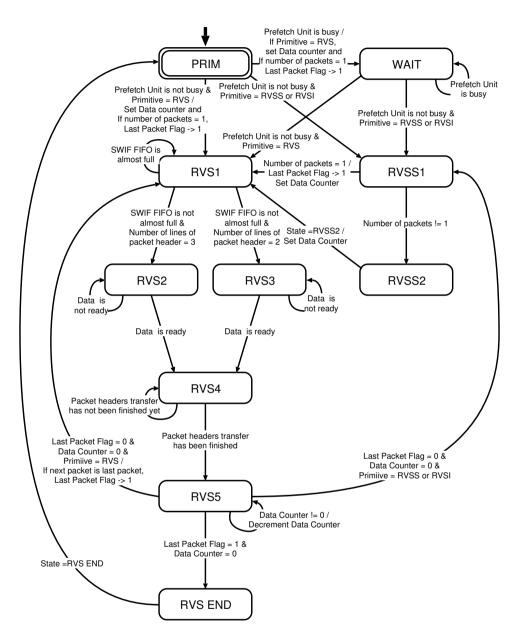

|            | 5.3.7 RVS 系プリミティブ処理時の状態遷移            |       |

|------------|--------------------------------------|-------|

|            | 5.3.8 IPUSH 系プリミティブ処理時の状態遷移          |       |

| 5.4        | Status Write Unit                    |       |

| 5.5        | ハードウェア量                              | . 86  |

| 第6章        | 基本通信性能の評価                            | 90    |

| 6.1        | 評価環境                                 | . 90  |

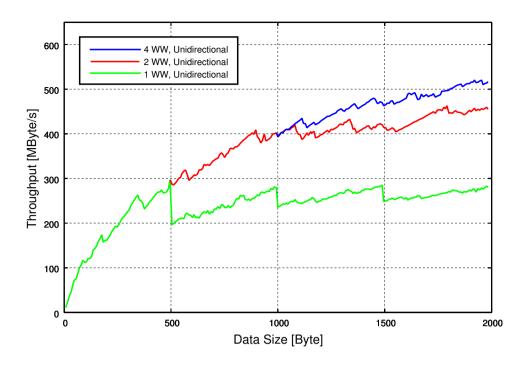

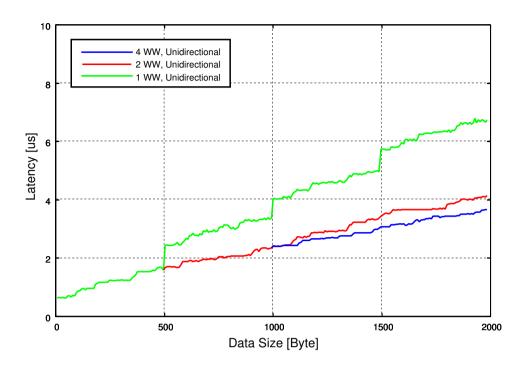

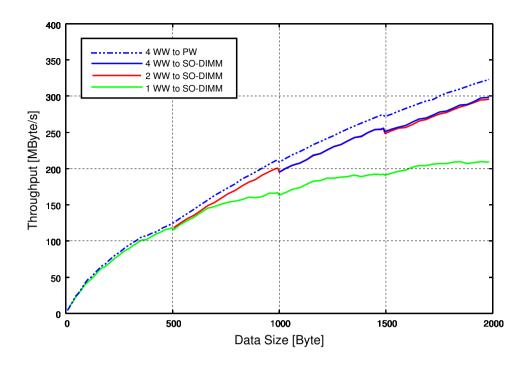

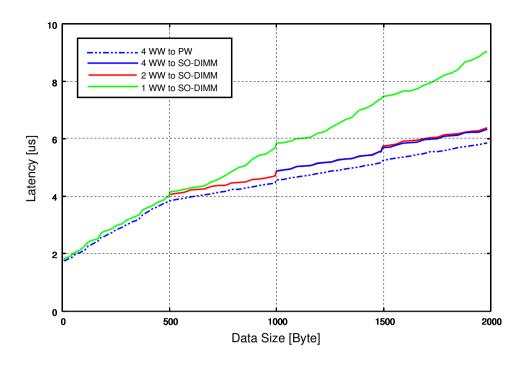

| 6.2        | BOTF                                 | . 90  |

|            | 6.2.1 片方向通信性能                        | . 91  |

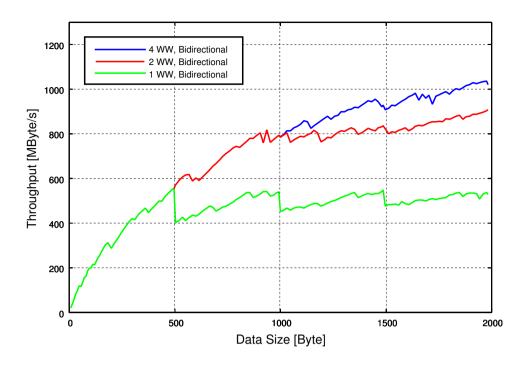

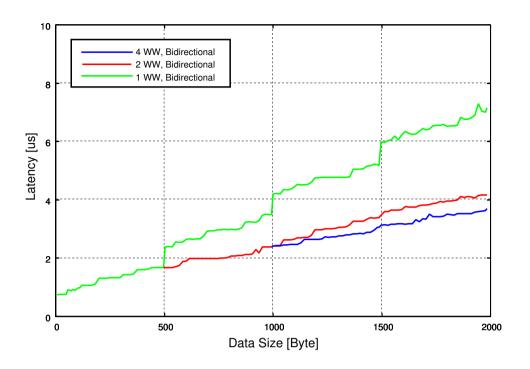

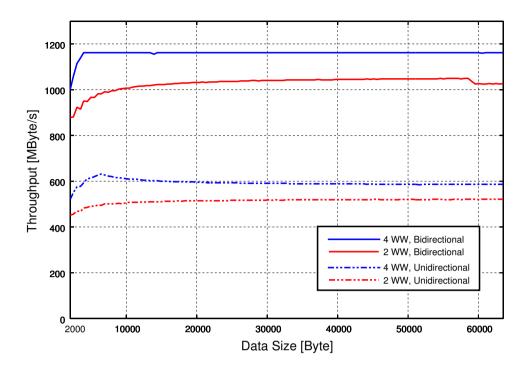

|            | 6.2.2 双方向通信性能                        | . 93  |

|            | 6.2.3 受信処理を含めた BOTF の通信性能            |       |

|            | 6.2.4 BOTF の最大スループット                 | . 95  |

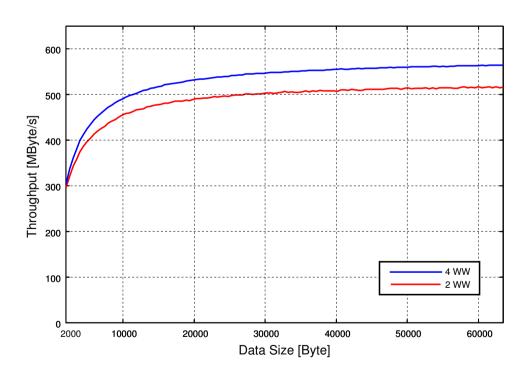

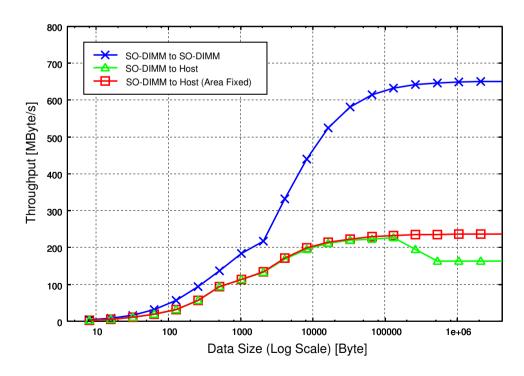

| 6.3        | SO-DIMM 間転送                          |       |

|            | 6.3.1 片方向,及び双方向の通信性能                 |       |

|            | 6.3.2 受信処理を含めた SO-DIMM 間転送の通信性能      | . 97  |

| 第7章        | メッセージ通信支援機構                          | 101   |

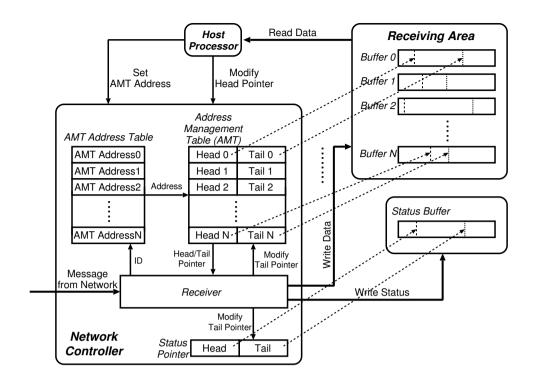

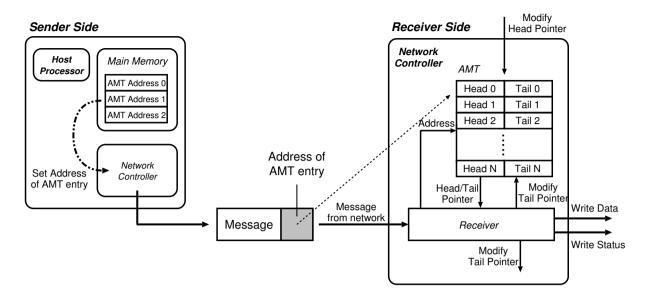

| 7.1        | IPUSH (Indirect PUSH)                | . 101 |

|            | 7.1.1 先行研究との差異                       | . 101 |

|            | 7.1.2 IPUSH 機構の設計                    | . 102 |

|            | 7.1.3 IPUSH 機構の概観                    | . 103 |

|            | 7.1.4 メッセージ受信領域の削減                   | . 106 |

|            | 7.1.5 IPUSH 機構の DIMMnet-2 への実装       | . 107 |

|            | 7.1.6 IPUSH 機構の評価                    | . 111 |

| 7.2        | LHS (Limited-length Head Separation) | . 112 |

|            | 7.2.1 LHS 機構の設計と実装                   | . 112 |

|            | 7.2.2 LHS 機構の評価                      | . 114 |

| 7.3        | まとめ                                  | . 116 |

| 笠 0 立      | #+÷△                                 | 117   |

| 第8章        | 結論<br>本研究のまとめ                        |       |

| 8.1        | 本研究のまとの                              |       |

| 8.2<br>8.3 | かけに                                  |       |

| 8.3        | のわりに                                 | . 119 |

| 謝辞         |                                      | 120   |

| 参考文献       | t                                    | 121   |

| 論文目錄       | <b>录</b>                             | 129   |

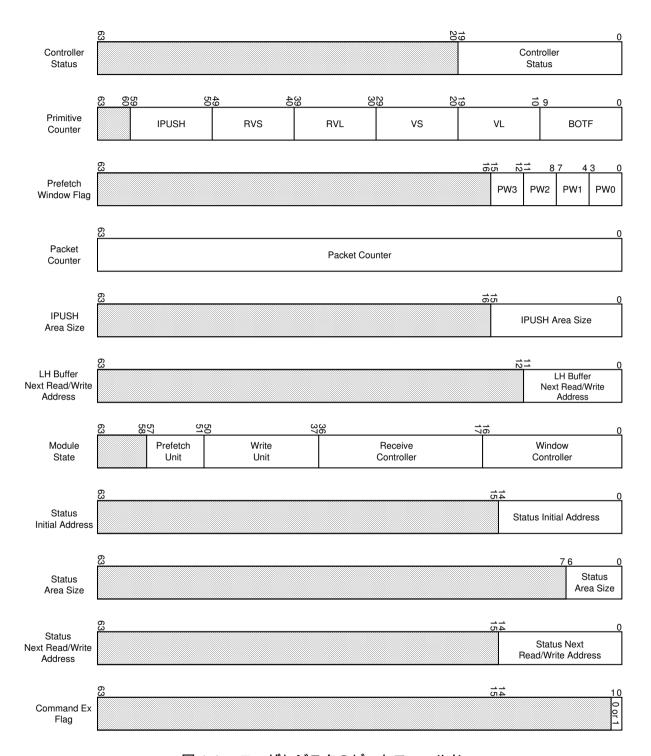

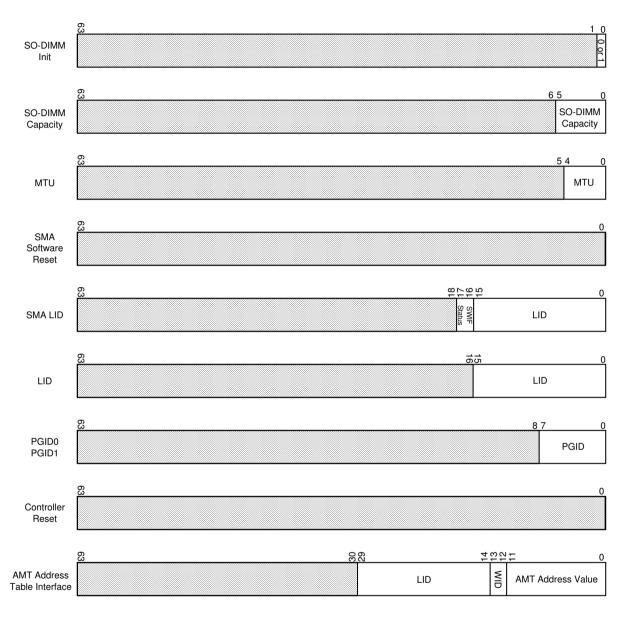

| 付録A        | 要求発行レジスタ以外の User Register のビットフィールド  | 133   |

| 付録B        | System Register のビットフィールド            | 137   |

| 付録C | DIMMnet Shell マニュアル   | 139 |

|-----|-----------------------|-----|

| C.1 | 概要                    | 39  |

| C.2 | ファイル構成                | 39  |

| C.3 | dsh の実行               | 39  |

|     | C.3.1 evpbuf_read     | 39  |

|     | C.3.2 h (or help)     | 40  |

|     | C.3.3 llcm_read       | 40  |

|     | C.3.4 llcm_write      | 40  |

|     | C.3.5 prim            | 41  |

|     | C.3.6 pw_read         | 42  |

|     | C.3.7 q (or quit)     | 42  |

|     | C.3.8 rllcm_write     | 42  |

|     | C.3.9 sreg_read       | 42  |

|     | C.3.10 sreg_write     | 43  |

|     | C.3.11 ureg_read      | 43  |

|     | C.3.12 ureg_write     | 44  |

|     | C.3.13 v (or version) | 45  |

|     | C.3.14 ww_write       | 45  |

# 表目次

| 2.1  | 転送されるメッセージサイズと個数                                     | 25  |

|------|------------------------------------------------------|-----|

| 2.2  | 各インターコネクトの比較                                         | 29  |

| 3.1  | DIMMnet-1 の主な仕様                                      | 31  |

| 4.1  | ホストインタフェース部の各モジュールのアクセス属性と MTRR の設定                  |     |

| 4.2  | 各バッファ間のデータ転送                                         | 46  |

| 4.3  | ホストインタフェース部のメモリ領域のアドレス割り当て                           | 49  |

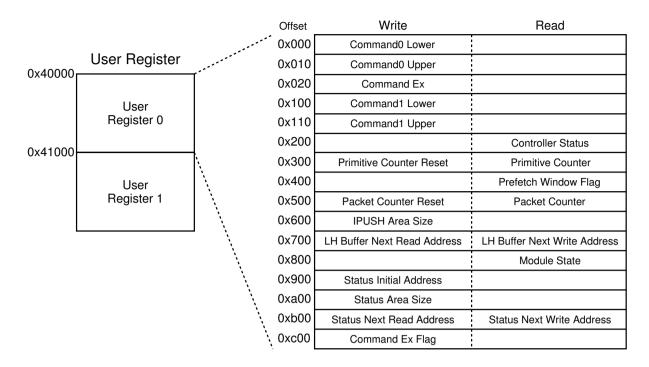

| 4.4  | 要求発行時のパラメータ                                          | 54  |

| 4.5  | DTYPE とデータ 1 要素のサイズの関係                               | 55  |

| 4.6  | LID と CLID の対応                                       | 55  |

| 4.7  | BOTF 時の要求発行パラメータ                                     | 56  |

| 4.8  | 要求発行レジスタ以外の User Register の用途                        | 57  |

| 4.9  | パケット受信ステータスで書き換えられる情報                                | 58  |

| 4.10 | SO-DIMM Capacity                                     | 59  |

| 4.11 | MTU                                                  | 59  |

| 4.12 | System Register の用途                                  | 61  |

| 4.13 | プリミティブ一覧                                             | 62  |

| 4.14 | ライン識別子                                               | 67  |

| 4.15 | パケットヘッダのパラメータ                                        | 68  |

| 5.1  | 有効ビット                                                | 74  |

| 5.2  | DIMMnet-2 ネットワークインタフェースコントローラのハードウェア量                | 87  |

| 6.1  | 評価環境                                                 | 90  |

| 6.2  | ヘッダ 16Byte, データ 496Byte 転送時のホスト側と Core Logic 側のレイテンシ | 92  |

| 7.1  | MPI レベルのレイテンシの内訳 (単位:μs)                             |     |

| 7.2  | IPUSH 機構に追加するテーブル                                    | 104 |

| 7.3  | IPUSH 機構における受信領域削減効果                                 | 107 |

| 7.4  | PUSH パケット (24Byte) の受信処理の詳細                          | 109 |

| 7.5  | IPUSH パケット (24Byte) の受信処理の詳細                         | 110 |

| A.1  | コントローラステータス                                          | 134 |

| A.2  | Primitive Counter                                    | 135 |

| A.3  | Prefetch Window Flag                                 | 135 |

| A.4  | Module State の詳細                                     | 135 |

| A 5  | Status Area Size                                     | 135 |

| C.1 | dsh で利用可能なコマンド                |  | <br> |  |  |  |  |  |  |  |  |  | . 1 | 141 |

|-----|-------------------------------|--|------|--|--|--|--|--|--|--|--|--|-----|-----|

| C.2 | sreg_write の [Option] で指定可能な値 |  |      |  |  |  |  |  |  |  |  |  | . 1 | 147 |

| C.3 | ureg_read の [Option] で指定可能な値  |  |      |  |  |  |  |  |  |  |  |  | . 1 | 147 |

| C.4 | ureg_write の [Option] で指定可能な値 |  |      |  |  |  |  |  |  |  |  |  | . 1 | 148 |

# 図目次

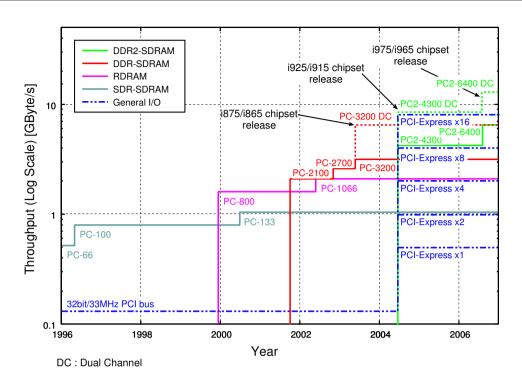

| 1.1  | メモリバスと I/O バスの進化                                   | 2  |

|------|----------------------------------------------------|----|

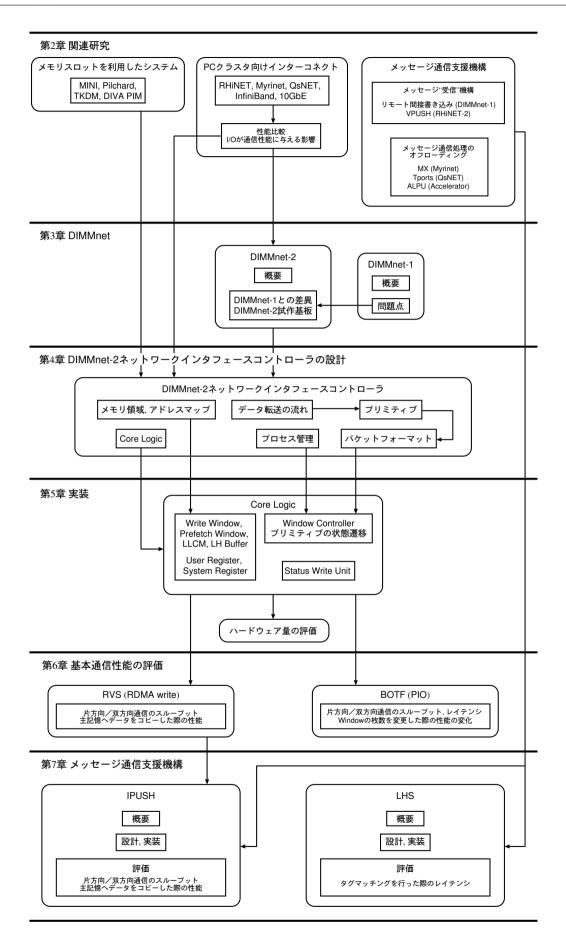

| 1.2  | 各章の関係                                              | 5  |

| 2.1  | MINI Architecture                                  | 7  |

| 2.2  | Pilchard Architecture                              | 8  |

| 2.3  | TKDM Architecture                                  | 9  |

| 2.4  | DIVA PIM Architecture                              | 9  |

| 2.5  | ゼロコピー通信                                            | 11 |

| 2.6  | LASN によるフロア内 PC 接続時の概観                             | 12 |

| 2.7  | Martini のブロック図                                     | 14 |

| 2.8  | RHiNET のソフトウェアレイヤ                                  | 14 |

| 2.9  | Myrinet-2000 ネットワークインタフェースのブロック図                   | 15 |

| 2.10 | 16×16 のクロスバスイッチを多段結合して Fat-Tree を構築した Myrinet の結合網 | 16 |

| 2.11 | Elan3 のブロック図                                       | 19 |

| 2.12 | Elan4 のブロック図                                       | 20 |

| 2.13 | InfiniBand のプロトコル階層                                | 21 |

| 2.14 | スループットの上昇曲線                                        | 24 |

| 2.15 | ALPU のブロック図                                        | 30 |

| 2.16 | Cell Block のブロック図                                  | 30 |

| 3.1  | DIMMnet-1 の基本構造                                    | 32 |

| 3.2  | DIMMnet-1                                          | 33 |

| 3.3  | 間接アクセス方式                                           | 34 |

| 3.4  | 不連続アクセス機構                                          | 35 |

| 3.5  | DIMMnet-2 試作基板の構成図                                 | 36 |

| 3.6  | DIMMnet-2 試作基板                                     | 37 |

| 3.7  | Dual Channel 動作への対応                                | 39 |

| 4.1  | コントローラ部のブロック図                                      | 41 |

| 4.2  | Core Logic 部のブロック図                                 | 42 |

| 4.3  | 各バッファ間のデータ転送                                       | 47 |

| 4.4  | PID-LID/WID table                                  | 49 |

| 4.5  | WID-PGID table                                     | 49 |

| 4.6  | パケットの送出処理時の各 ID の取得                                | 50 |

| 4.7  | ホストインタフェース部のメモリ領域のアドレスマップ                          | 51 |

| 4.8  | Write Window のアドレスマップ                              | 52 |

| 4.9  | Prefetch Window のアドレスマップ                     | 52 |

|------|----------------------------------------------|----|

| 4.10 | LLCM のアドレスマップ                                | 52 |

| 4.11 | LH Buffer のアドレスマップ                           | 52 |

| 4.12 | User Register のアドレスマップ                       | 53 |

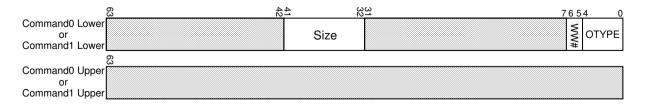

| 4.13 | 要求のフィールドフォーマット                               | 53 |

| 4.14 | BOTF 時の要求発行のフィールドフォーマット                      | 55 |

| 4.15 | System Register                              | 58 |

| 4.16 | SO-DIMM Address (512MByte/module)            | 60 |

| 4.17 | 連続ロード                                        | 63 |

| 4.18 | ストライドロード (Iteration=4)                       | 63 |

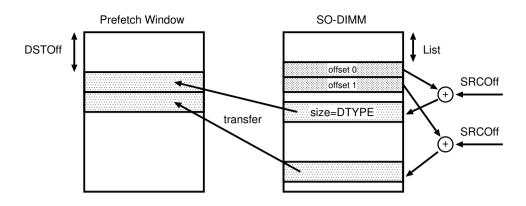

| 4.19 | リストロード (Iteration=2)                         | 64 |

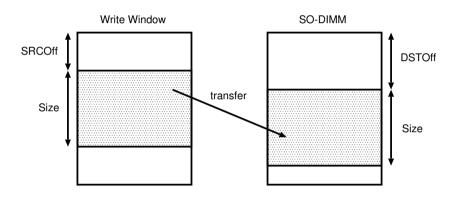

| 4.20 | 連続ストア                                        | 64 |

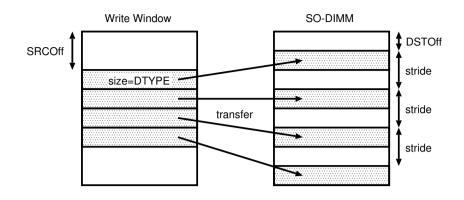

| 4.21 | ストライドストア (Iteration=4)                       | 65 |

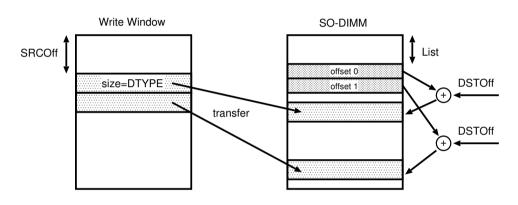

| 4.22 | リストストア (Iteration=2)                         | 65 |

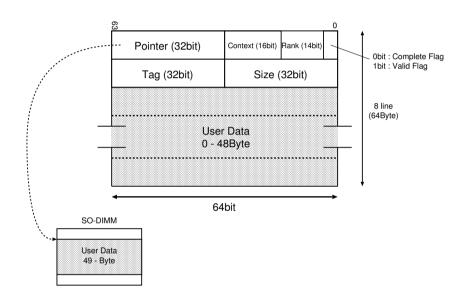

| 4.23 | パケットフォーマット                                   | 66 |

|      |                                              |    |

| 5.1  | Write Window, Prefetch Window, LLCM の構造      |    |

| 5.2  | Write Window の構造                             |    |

| 5.3  | Prefetch Window の構造                          |    |

| 5.4  | LLCM の構造                                     |    |

| 5.5  | LH Buffer の構造                                |    |

| 5.6  | ホスト – レジスタ間の入出力                              |    |

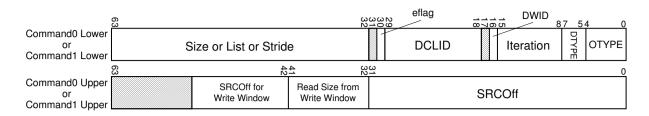

| 5.7  | User Register から転送するプリミティブのフィールドフォーマット       |    |

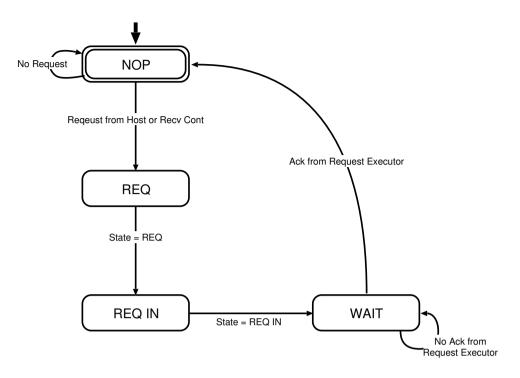

| 5.8  | Window Controller の構成                        |    |

| 5.9  | Request Acceptor の状態遷移図                      |    |

|      | Request Executor                             |    |

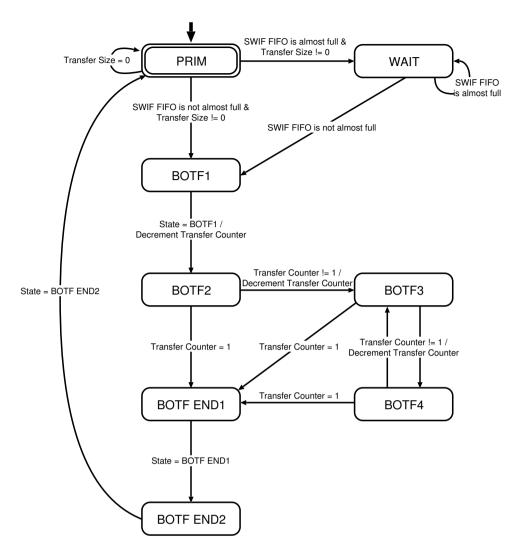

|      | BOTF の状態遷移図                                  |    |

|      | VL 系プリミティブの状態遷移図                             |    |

|      | VS 系プリミティブの状態遷移図                             |    |

|      | RVL 系プリミティブの状態遷移図                            |    |

|      | RVS 系プリミティブの状態遷移図                            |    |

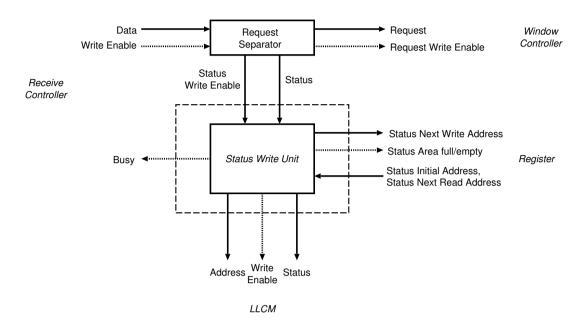

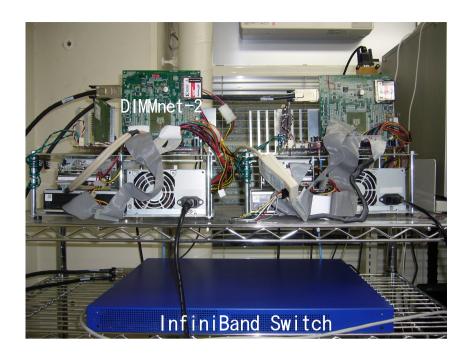

|      | Status Write Unit と周辺モジュールの構造                |    |

| 5.17 | Status Write Unit の状態遷移図                     | 89 |

| 6.1  | 評価環境の概観                                      | 91 |

| 6.2  | BOTF のオーバラップ                                 | 92 |

| 6.3  |                                              | 93 |

| 6.4  | BOTF レイテンシ (片方向)                             |    |

| 6.5  | V /                                          | 95 |

| 6.6  |                                              | 96 |

| 6.7  | 受信処理を含めた BOTF のスループット                        | 90 |

| 6.8  | 受信処理を含めた BOTF の人ルーノット                        |    |

|      | BOTF スループット (データサイズ:2KByte 以上)               |    |

| 6.9  | DOII ヘルーノット (ノーフッイへ・2NDyに以上)・・・・・・・・・・・・・・・・ | 77 |

| 6.10         | 受信処理を含めた BOTF のスループット (データサイズ: 2KByte 以上) 99 | 9 |

|--------------|----------------------------------------------|---|

| 6.11         | SO-DIMM 間通信 スループット                           | 0 |

| 6.12         | 受信処理を含めた SO-DIMM 間通信                         | 0 |

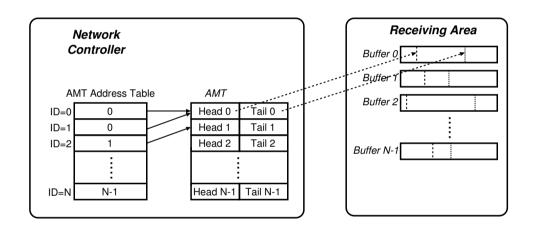

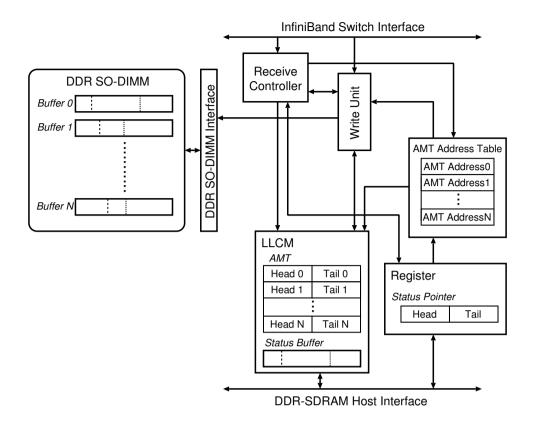

| 7.1          | IPUSH 機構                                     | 3 |

| 7.2          | AMT Address Table を用いない IPUSH 機構             | 5 |

| 7.3          | AMT Address Table の設定例                       | 5 |

| 7.4          | IPUSH 機構の実装                                  |   |

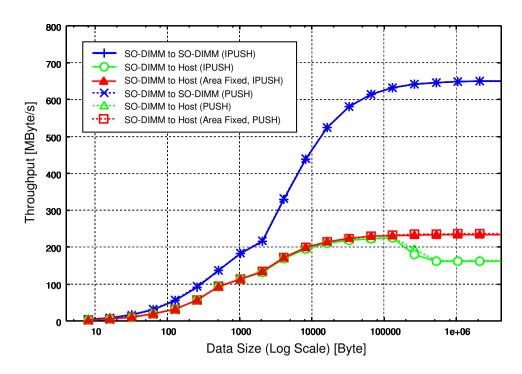

| 7.5          | PUSH と IPUSH のスループットの比較                      | 1 |

| 7.6          | LHS を利用する際のメッセージフォーマット                       |   |

| 7.7          | LH Buffer に格納されたメッセージのフォーマット                 | 3 |

| 7.8          | IPUSH with LHSv2 のプリミティブフォーマット               | 4 |

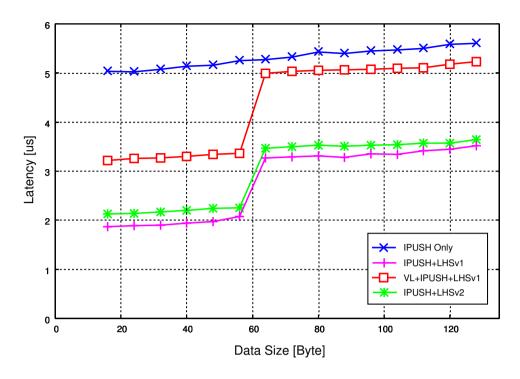

| 7.9          | LHS 機構によるレイテンシの変化                            | 6 |

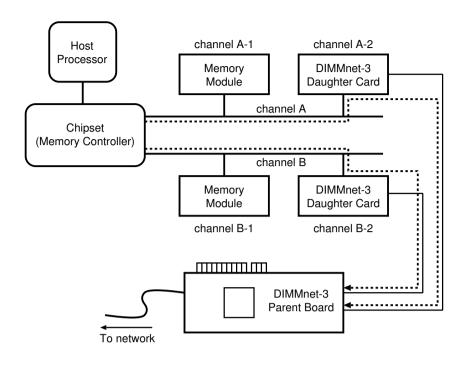

| 8.1          | DIMMnet-3 概観                                 | 9 |

| A.1          | ユーザレジスタのビットフィールド                             | 6 |

| B.1          | システムレジスタのビットフィールド135                         | 8 |

| <b>C</b> .1  | dsh を構成するファイル                                | 0 |

| C.2          | dsh の書式と実行例14                                | 1 |

| C.3          | evpbuf_read の書式と実行例142                       | 2 |

| C.4          | help の書式と実行例                                 | 3 |

| C.5          | llcm_read の書式と実行例                            | 3 |

| C.6          | llcm_write の書式と実行例14                         | 4 |

| C.7          | prim の書式と実行例                                 | 5 |

| C.8          | pw_read の書式と実行例                              |   |

| C.9          | rllcm_write の書式と実行例                          | 6 |

| <b>C</b> .10 | sreg_read の書式と実行例                            | 6 |

| C.11         | sreg_write の書式と実行例                           | 6 |

|              | ureg_read の書式と実行例                            |   |

| C.13         | ureg_read で module_state を指定した場合の表示          | 8 |

|              | ureg_write の書式と実行例149                        |   |

|              | version の実行例                                 |   |

| C.16         | ww_write の書式と実行例                             | 0 |

# 第1章 緒論

近年、ベクトル型スーパーコンピュータに代わり、スカラ型プロセッサを多数用いた高性能なシステムが企業や研究機関で計算資源の主流となっている。中でも、汎用の PC (Personal Computer)を多数、相互に接続した PC クラスタシステムの躍進は目覚しく、このことは世界中のスーパーコンピュータの性能をランキングした Top500[1] にランクインしているシステムの割合の、ここ数年の推移を見ると明らかである。

PC クラスタが多く用いられている背景には、PC 市場の発展による量産効果と搭載される CPU の著しい性能向上から高性能な PC が安価に入手可能となり、低コストに高性能なシステムを構築可能になったということが挙げられる.

こういった PC クラスタの PC 間の接続に用いられるインターコネクトには Gigabit Ethernet のような汎用的なネットワークのほか, Myrinet[2], QsNET (Quadrics NETwork)[3], InfiniBand[4] といった PC クラスタ専用のインターコネクトが存在する.

PC クラスタ専用のインターコネクトは、SAN (System Area Network) と呼ばれ、RDMA (Remote Direct Memory Access) 転送のサポートや、低レイテンシでデータの転送が可能なネットワークスイッチ、ハードウェアによる Collective 通信のサポートなどにより、汎用的なネットワークよりも高い性能を達成している。これらインターコネクトのネットワークインタフェースは、通常 64bit/133MHzの PCI-X バスや PCI-Express[5] に装着され、近年では 10Gbps クラスのネットワークを構築することが可能になっている。

ネットワークインタフェースが装着される I/O バスは PCI-Express や HyperTransport[6] の登場により、PCI バスに比べて性能が飛躍的に向上した. 特に、PCI-Express は 2005 年頃には AGP (Accelerated Graphics Port) バスにとって代わり、グラフィックスデバイス向けに汎用 PC に搭載され、現在では PCI バスに代わる汎用 I/O バスとしての地位を築きつつある. しかし、これらの I/O バスの登場以前は、汎用 PC においては 32bit/33MHz の PCI バスが主流であり、PCI バスの最初のバージョンである PCI 1.0[7] が策定されてから 10 年以上が経過していた.

図 1.1 に汎用 PC における I/O バスとメモリの進化を時系列で示す. 図 1.1 は Intel 製の PC 向けチップセットでサポートしているメモリや I/O を元にしたものであり、それ以外のチップセットベンダの製品やサーバ向けの製品は対象外としている。メモリの規格もすべてを記載しておらず $^{(\dot{z}-1)}$ 、代表的な値のみをプロットしている。また、PCI-Express は双方向のスループットを示している。この図から、PCI-Express 登場以前は  $32 \mathrm{bit}/33 \mathrm{MHz}$  PCI バスとメモリバスとの性能差が拡大し続けていたことが分かる。特に、チップセットが i875/i865 の世代になると、Dual Channel でのメモリアクセスをサポートするようになり、性能差は一段と拡大した。 2004 年になると DDR2-SDRAM、及びPCI-Express をサポートした i925/i915 チップセットが市場に登場したが、当初 16 レーン  $(x16)^{(\dot{z}-2)}$ の

$<sup>^{(</sup>$ 注  $^{1)}}$ PC-1600 DDR-SDRAM や PC-600/700 RDRAM など

$<sup>^{(\</sup>dot{z}\ 2)}$ PCI-Express は片方向 2 本のシリアル差動信号方式で伝送を行う. 従って, 双方向で 4 本の信号線を用いる. この 4 本の信号線を基本単位  $(1\ \nu-\nu\ (x1))$  とする.  $1\ \nu-\nu$ 当たり, 片方向 2.5Gbps (双方向 5.0Gbps) の伝送速度を持つ  $(8B10B\ x)$ コーディングにより実効速度は片方向 2.0Gbps, 双方向 4.0Gbps).  $16\ \nu-\nu$ は  $1\ \nu-\nu$ の信号線を 16 組束 ねたものである.

第 1 章 緒論 2

図 1.1 メモリバスと I/O バスの進化

PCI-Express はグラフィックスデバイス専用という位置付けであり、グラフィックスデバイス以外のデバイスを接続すると 1 レーン (x1) のモードで動作するという代物であった [8][9]. i975/i965 からグラフィックデバイス以外のデバイス向けに 4 レーン (x4) や 8 レーン (x8) のポートがマザーボードに搭載されるようになってきた.

このように、PC における汎用 I/O バスの進化の速度は遅く、プロセッサやメモリの性能が向上するにつれて、汎用 PC を用いて PC クラスタを構築すると PCI バスがボトルネックになるという問題が存在した。一部では PCI バスを拡張した 64bit/66MHz PCI バスや、上位規格の PCI-X バスが採用され、32bit/33MHz PCI バスの 4 倍以上のスループットを示していたが、これらは主にサーバやワークステーションにのみ搭載されていた。そのため、高性能な PC クラスタの構築には汎用 PC ではなく、これらの高速な I/O バスを持つシステムが用いられたが、これらは一般的に PC より高コストであり、PC クラスタの利点の一つであるコストパフォーマンスの高さを損なう結果となった。

そこで、MEMOnet[10] と呼ばれるネットワークインタフェースのクラスが 1999 年に提案された。MEMOnet は "主記憶を搭載するメモリスロットに接続するネットワークインタフェース" と定義されており、32bit/33MHz の PCI バスしか搭載されていない低コストな汎用 PC 上でメモリバスのスループットに近い通信性能を実現することを目的としている.

メモリバスは汎用 I/O バス (32bit/33MHz PCI バス) よりもスループットが高く, アクセスレイテンシも低いため, 通信性能が向上すると期待できる. また, 性能向上の速度も汎用 I/O バスより高く, ボトルネックになりにくいという利点がある. さらに, メモリスロットはほぼすべての汎用 PC に搭載されているため, サーバやワークステーションを用いずとも, 上記の利点による恩恵を受けることができ, PC クラスタの構築コストを抑えることが可能となる.

本論文の研究対象である DIMMnet-2 は, DIMM (Dual Inline Memory Module) スロットに装着する MEMOnet として定義される DIMMnet の実装例である.

第 1 章 緒論 3

## 1.1 DIMMnet-2 プロジェクト

DIMMnet-2 プロジェクトは, 総務省の戦略的情報通信研究開発推進制度 (SCOPE) のプロジェクトの一環として, 東京農工大学中條研究室 (東京農工大), 株式会社 東芝 研究・開発センター, 慶應義塾大学天野研究室 (慶大), 和歌山大学國枝研究室(注 3)によって, 2002 年度に立ち上げられた. 総務省のプロジェクトは 2006 年度で終了したものの, それ以後も上記の研究機関によって研究は続けられている.

DIMMnet-2 は 184pin DDR-SDRAM スロットに装着する. 基板設計は慶大と東京農工大,株式会社 日立情報通信エンジニアリング (日立 JTE) (注 4) によって行われた [11][12][13]. 2003 年度に設計,及び製造した基板は,2004 年度より稼働を開始し,慶大と東京農工大が中心となり,ネットワークインタフェースコントローラの設計,実装といったハードウェア部分の開発を行った [14][15]. 一方,和歌山大学では分散共有メモリシステムの開発が行われた.

2005 年度以降は DIMMnet-2 の基本通信性能の評価やメッセージ通信支援機構の実装 [16][17] などが行われ、これを利用した MPI (Message Passing Interface) が実装された [18]. しかしながら、通信性能の評価を通じて、ホストから DIMMnet-2 に対してバースト転送でデータを読み書きすると、意図しないデータが読み書きされるという現象が明らかになり、アプリケーションレベルでの評価を行うのが難しい状況となった。 メモリバスへの供給クロックを落とすなどの対策がとられたが、完全な解決には至っていない。

本プロジェクトの期間に, PC におけるメモリバスが DDR-SDRAM バスから DDR2-SDRAM バスに移行したことを受け, 2006 年度より DDR2-SDRAM スロットに装着する DIMMnet-3 の開発が開始された. 2007 年 7 月の時点で, 基板の設計, 及び製造が完了している.

# 1.2 DIMMnet-2 プロジェクトにおける筆者の貢献

筆者は 2004 年度より DIMMnet-2 の開発に加わった. 当時, DIMMnet-2 試作基板が完成したばかりの時期であった. 筆者は DIMMnet-2 のプロジェクトにおいて, 慶大側で中心的な立場にあり, ネットワークインタフェースコントローラの開発を主導した.

DIMMnet-2 では通信遅延を削減するために、ネットワークインタフェースコントローラにおける処理をすべてハードワイヤードロジックで実装する方針とした。そのため、プリミティブと呼ばれる、ネットワークインタフェースコントローラで実行される基本命令や、その動作など、ネットワークインタフェースコントローラのアーキテクチャの検討、及び決定を行った。2004年に実装したネットワークインタフェースコントローラには、後に機能拡張を行ったが、基本的な構成は変更していない。これは、アーキテクチャ検討の際に、機能ごとにモジュール化し、機能追加の際には最小限の変更で済むような構成を採ったことが功を奏したと言える。

2005 年度以降は基本通信性能の評価とネットワークインタフェースコントローラの高機能化を行った. 基本通信性能の評価では, PIO (Programmed Input/Output) 通信機構である BOTF (Block On-The-Fly) やネットワークインタフェース上のメモリ間転送のスループットとレイテンシを測定した. 評価の結果, BOTF の通信性能が Myrinet などの PC クラスタ向けインターコネクトにおける RDMA に匹敵する通信性能を持つことを示した.

ネットワークインタフェースコントローラの高機能化においては、メッセージ通信を支援するための通信機構である IPUSH と LHS の設計、及び実装を行った. MPI などのメッセージ通信をこれ

<sup>(</sup>注 3)後,立命館大学國枝研究室

<sup>(</sup>注 4) 当時, 日立インフォメーションテクノロジー (日立 IT)

第1章緒論 4

らの通信機構を用いて実装することで低レイテンシな通信を実現可能であることを示した. また、DIMMnet-2 のデバッグツールとして、DIMMnet-2 を対話的に操作できる dsh (DIMMnet Shell) を開発し、実機を用いた動作確認のための環境を整備した.

## 1.3 本論文の構成

図 1.2 に本論文の各章の関係を示す。2 章で DIMMnet-2 に関連のある研究として、メモリスロットを機能拡張に用いる種々のシステム、PC クラスタ向けインターコネクト,及びメッセージ通信を支援する通信機構について述べる。3 章では第一世代の DIMMnet である DIMMnet-1 と、研究対象である DIMMnet-2 の概要を述べる。4 章と 5 章では DIMMnet-2 ネットワークインタフェースコントローラの設計と実装についてそれぞれ述べる。6 章では 5 章で実装したネットワークインタフェースコントローラの基本通信性能を示し、7 章ではメッセージ通信支援機構の評価を示す。そして、8 章で本研究をまとめる。

付録として, 付録 A と付録 B ではネットワークインタフェースコントローラ内部のレジスタのビットフィールドを, 付録 C では dsh のマニュアルを掲載する.

第1章緒論 5

図 1.2 各章の関係

# 第2章 関連研究

本章では DIMMnet に関連する事例についてまとめる. まず, DIMMnet と同様に, メモリスロットを機能拡張に用いる様々なシステムについて述べる. 続いて, PC クラスタ向けインターコネクトについて触れる. ここでは DIMMnet に関係が深いインターコネクトである RHiNET, 及び商用のインターコネクトとして代表的な Myrinet, QsNET, InfiniBand についてまとめる. 最後に並列処理に用いられているメッセージ通信を支援する通信機構について述べる.

本研究ではこれらの事例の問題点や通信性能に影響を与える要件をもとにして, DIMMnet-2 ネットワークインタフェースコントローラの設計, 及び実装を行っていく.

## 2.1 メモリスロットを機能拡張に用いるシステム

本節ではメモリスロットを汎用 I/O バスのように機能拡張のために利用するシステムについて述べる. これらのシステムがホストプロセッサから, どのように利用可能であるのかを示し, その問題点をまとめる.

#### 2.1.1 MINI

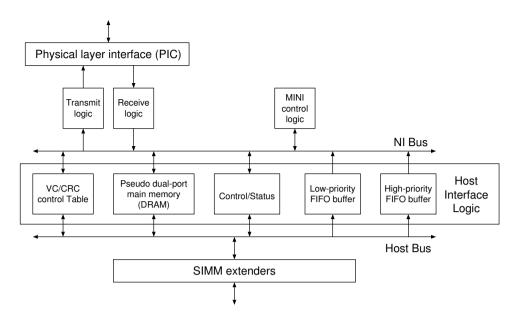

MINI (Memory-Integrated Network Interface) は Minnich らによって提案された, SIMM extender を介して 72pin SIMM バスに接続するネットワークインタフェースである [19].

MINI は並列分散処理向けに,

- 単一の ATM (Asyncronous Transfer Mode) のセルを 1μs のレイテンシで転送

- 1Gbps のスループット

- ゼロコピー通信 (2.2 節) を利用した TCP/IP, 及び NFS (Network File System) の実現

といったことを目標に開発された. MINI は単一の ATM のセルを 400ns でネットワークに送出することが可能であり、ホストの処理を含めた RTT (Round Trip Time) は  $3.9\mu$ s であった.

図 2.1 に MINI のブロック図を示す. Host Interface Logic 上にメモリや制御ロジックなどが搭載されており, これらはホストプロセッサから直接アクセス可能である.

#### 2.1.2 Pilchard

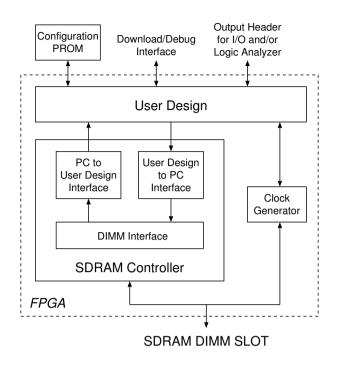

Pilchard は Leong らによって開発された, FPGA (Field Programmable Gate Array) を搭載した Reconfigurable Computing 用のシステムである [20][21]. Pilchard は PC の 168pin SDR-SDRAM バスに接続する. 対応するバスクロックは PC100, 及び PC133 である.

図 2.1 MINI Architecture

CPU や FPGA の性能が向上するにつれて, 汎用 I/O バスである PCI バスとの性能差が拡大する. そのため, PCI バス接続型の Reconfigurable Computing システムでは PCI バスがボトルネックとなり, 高い性能が得られないことを背景として Pilchard は開発された.

PC においては、チップセットが SPD (Serial Presence Detect) インタフェースを持つようになり、BIOS (Basic Input/Output System) がメモリの情報をメモリモジュール上の SPD ROM から読み出すことでメモリの検出や設定を行うようになった. しかし、Pilchard は SPD ROM を持っていないため、PC の起動時には Pilchard は検出されない. そこで、PC 起動後にチップセットのレジスタを書き換えることで Pilchard を利用可能にしている.

図 2.2 に Pilchard のブロック図を示す.

ユーザプログラムは UNIX の mmap システムコールを用いて, Pilchard のインタフェースを自プロセスのアドレス空間にマップする. このようにすることで, 一度マッピングすれば, システムコールを介することなく, Pilchard を扱うことが可能になる.

Pilchard では DIMM インタフェースの領域を read 用と write 用に分けている。これは、ホストから Pilchard へのアクセスを最適化するためである。Pentium Pro 以降の Intel 製プロセッサでは MTRR (Memory Type Range Register) (注 1)を利用して、ページ単位でメモリアクセスの挙動を制御可能である。そのため、write 用の領域を Write Combining 属性、read 用の領域を Uncachable 属性に設定することで、書き込み時に Pilchard に対して高いスループットを得ることができる。

Write Combining 属性に設定した場合の Pilchard への書き込み時のスループットは PC100 のメモリバスを使用した際に 409.64MByte/s まで達しており、 32bit/33MHz の PCI バスの理論最大スループットの 4 倍近い性能を示している。一方、 read 領域が Uncachable 属性に設定されていることによって、 読み出し時のスループットは 52.8MByte/s 程度にとどまっている。

$<sup>^{(\</sup>dot{z}=1)}$ Pentium Pro 以降の IA32 アーキテクチャのプロセッサで利用可能な, プロセッサからメモリへのアクセス方式を制御するためのレジスタ

第2章 関連研究 8

図 2.2 Pilchard Architecture

#### 2.1.3 TKDM

TKDM はスイス連邦工科大学で開発された、PC の SDR-SDRAM スロットに装着するストリーミング処理向けのアクセラレータである [22]. 基板上に FPGA を搭載しており、これを用いてアプリケーションのアクセラレーションを行う. TKDM は Pilchard と同様に、汎用 I/O バスがボトルネックとなっていることを背景として開発された。図 2.3 に TKDM のプロック図を示す.

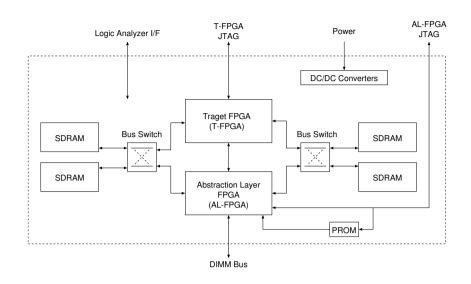

TKDM にはホストのメモリバスと接続する AL-FPGA (Abstraction Layer FPGA) と、ユーザの設計した論理を搭載する T-FPGA (Target FPGA) という 2 個の FPGA が搭載される。これにより、T-FPGA にホストのメモリバスのインタフェースを搭載する必要がなくなるため、ユーザが利用可能なリソースを多く確保することができるという利点がある。 さらに、ボード上に 4 枚の SDRAM が搭載されており、Bus Switch を切り替えることで AL-FPGA と T-FPGA が同時に SDRAM を利用することが可能になっている。 Bus Switch の切り替えは AL-FPGA から行い、ホストからは AL-FPGA を介して、SDRAM にアクセス可能である。

TKDM は Pilchard 同様, PC の起動時には BIOS から検出されないため, PC の起動後にチップセットの設定を変更することで, TKDM を利用可能にしている. また, この変更と同時に TKDM のホストからアクセス可能な領域を Uncachable 属性に設定している. このことにより, TKDM に対するアクセスのスループットは書き込み時に 128MByte/s, 読み出し時に 53MByte/s 程度にとどまっている.

#### **2.1.4 DIVA PIM**

DIVA PIM (Data IntensiVe Architecture Processing-In-Memory) はプロセッサとメモリの速度の ギャップを埋めるための手法である PIM ベースのシステムであり、USC/ISI で研究が行われてい

第2章 関連研究 9

☑ 2.3 TKDM Architecture

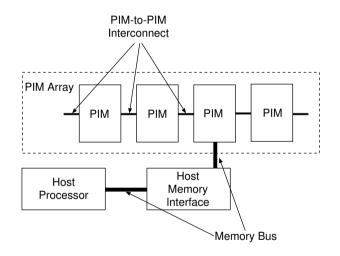

る. DIVA PIM はストリーミングデータを扱うマルチメディア系のアプリケーションなど, スループットが求められるアプリケーションを対象としたシステムである [23][24]. 図 2.4 に DIVA システムのアーキテクチャを示す.

図 2.4 DIVA PIM Architecture

ホストはメモリバスに接続された PIM によって相互に接続される. PIM を co-processor として用いるために, DDR-SDRAM スロット装着型の DIVA PIM チップを搭載した基板が開発されている.

#### 2.1.5 まとめ

本節で紹介したメモリスロット装着型のシステムは, いずれも汎用 I/O バスではスループットが不足するという問題を解決するために開発された.

しかし、Pilchard と TKDM はホストからアクセス可能な領域のすべて、または一部を Uncachable

属性にする必要があるため、汎用 I/O バスに対して大幅な性能向上は見られなかった。仮に、Pilchard の read 領域をホストの CPU にキャッシュされる Write Back 属性に設定した場合、読み出し時のスループットは向上する。しかし、一度 Pilchard の read 領域をキャッシュに格納すると、Pilchard 側から当該の read 領域を書き換えても CPU はキャッシュからデータを読み出すため、新しい値が反映されないという問題がある。そのため、Pilchard からデータを読み出すたびに CPU のキャッシュをフラッシュすることが必要となる。しかし、Pilchard は PentiumIII のシステムに搭載されており、PentiumIII のキャッシュフラッシュ命令を実行するとキャッシュの全領域がフラッシュされる。そのため、結果としてシステムの性能低下を招くことになる。

Intel 製の x86 命令セットのプロセッサでは, Pentium4 からキャッシュライン単位でキャッシュをフラッシュする CLFLUSH 命令が追加された. DIMMnet-2 では, この CLFLUSH 命令とメモリへのプリフェッチ命令である PREFETCHNTA 命令を利用することで, ホストから DIMMnet-2 に対する読み出し時に高いスループットを得ることができるようにしている.

また、MINIのように、基板上のメモリに対してホストから直接アクセス可能な形態を採用すると、メモリバスが高速になるに従って、システムを構築することが難しくなる。 MINI の場合は SIMM extender にネットワークインタフェースを装着するが、この場合、メモリバスからの物理的な距離が大きくなる。 近年の SDRAM の場合、RAS (Row Address Strobe) 信号を出してから一定クロック後に CAS (Column Address Strobe) 信号を出し、それから一定クロック後にデータの読み書きを行うということが仕様で定められているため、この制約を満たせなくなることが予想される。 このことから、 DIMMnet-2 では、ホストプロセッサから基板上のメモリに対して、コントローラ内部のバッファやレジスタを介して、間接的にアクセスする構造を採用した。 これにより、 基板に搭載するメモリの物理的な配置や容量 (枚数)の柔軟性が高まるという利点がある。

### 2.2 並列分散処理環境用インターコネクト

本節では PC クラスタなどの並列分散処理環境向けに開発されたインターコネクトについて述べる. 各インターコネクトの特徴をまとめ、その性能比較を行うことで、システムを構成する要素のうち、特に通信レイテンシに影響が大きい事柄を明らかにする.

一般に、高性能な並列分散処理環境用インターコネクトではユーザレベル通信とゼロコピー通信を実現することにより、汎用のネットワークである Fast Ethernet や Gigabit Ethernet より高スループット、低レイテンシな通信を行っている.

ユーザレベル通信 ユーザレベル通信とは、ユーザプロセスが通信を起動する際に OS のシステムコールを用いずに、ユーザ権限でデバイスに直接要求を出して通信を起動する方式である。 ユーザレベル通信を用いることで、システムコールの発行に伴う OS のオーバヘッドを除外し、通信が開始されるまでのレイテンシを大幅に低減することが可能となる.

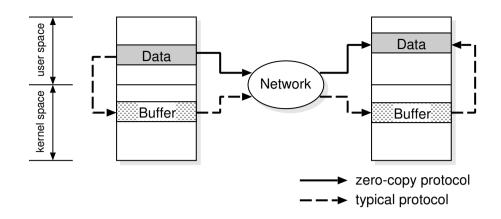

ゼロコピー通信 一般に、Ethernet などのネットワークを用いた通信では、送信データは一度、OS 上の送信バッファにコピーされ、ネットワークインタフェースは送信バッファからデータを送信する。受信側においても、ネットワークから到着したデータは一度、OS 上の受信バッファに蓄えられ、その後、受信バッファからユーザプロセスの領域にコピーされる。このメモリ間のデータコピーは PIO で行われるため、転送速度は極めて低く、通信オーバヘッドを大きくする要因の一つとなる.

ゼロコピー通信は、通信からメモリ間のデータコピーを排除した通信方式である. 予め転送デー

図 2.5 ゼロコピー通信

タが置かれた領域とデータを受信する領域を、各々ネットワークインタフェースに登録しておき、通信が発行されるとネットワークインタフェースがメモリとネットワークの間で DMA 転送を行うことでメモリ間のデータコピーを排除する.

一般的な通信とゼロコピー通信におけるデータの流れを図 2.5 に示す. 図 2.5 中の実線はゼロコピー通信のデータの流れを, 点線は一般的な送受信バッファを用いた通信のデータの流れを示している.

#### **2.2.1 RHINET**

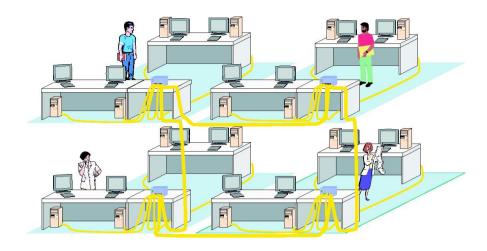

RHiNET[25][26] は本研究室と新情報処理開発機構が共同で開発した, LASN (Local Area System Netowrk)[27] というネットワーククラスのためのインターコネクトである.

一般の PC クラスタに用いられる SAN の場合, インターコネクトのトポロジやリンク長に制限があるため, システムを構成するノード (PC) は 1 箇所に集中して設置される. これに対し, LASNではオフィスの 1 フロアなど, ある程度の広さを持った空間に分散配置された PC を相互に結合し,並列分散処理環境を構築する.

このようなシステムを提案した背景として、近年の PC の価格対性能比の著しい向上から、高速な PC が数十~数百台規模でオフィスなどに導入されるようになったことが挙げられる。このような PC は 1 台 1 台がスーパーコンピュータの 1 PE (Processor Element) 相当の性能を持つに至っており、また、オフィスのような環境では事務処理などの比較的負荷の軽い処理が主な用途であるため、各 PC は計算資源に余裕があるものと考えられる。そこで、これらの PC を相互結合し、余剰計算資源を利用して分散並列処理を行うことによって、計算資源の有効利用を図るのが LASN の目的である。

LASN には LAN (Local Area Network) のような、トポロジやリンク長に対する柔軟性と SAN のような高い信頼性や通信性能が要求される.

図 2.6 に LASN を用いてフロア内の PC を接続した際の概観を示す.

LASN に要求される高スループットで低レイテンシな通信を実現するには、ハードウェアそのもののデータ転送能力を向上させることもさることながら、通信へのソフトウェアの介在を極力排除することが効果的である。RHiNET では、次の機能をハードウェアで提供することにより、ソフトウェアによるオーバヘッドを排除している。

図 2.6 LASN によるフロア内 PC 接続時の概観

- パケットの順序保証と, 通信エラーの回避を行うことで, 上位レイヤによる通信保証処理の オーバヘッドを排除

- 通信におけるプロテクション機構を設けた上でユーザレベル通信を用いることで, 通信起動 時の OS の介在によるオーバヘッドを排除

- RDMA を用いたゼロコピー通信を行うことで、ユーザメモリと送信バッファとの間のメモリ 間コピーによるオーバヘッドを排除

LASN では、これらを任意のトポロジで実現する. さらに、フロアレベルで分散配置された PC を相互接続すべく 100m ~ 1km 程度のリンク長をサポートする必要がある. RHiNET では、専用のネットワークスイッチと専用のネットワークインタフェースを開発し、伝送媒体に光ファイバを用いることで、これらを実現している.

RHINET のネットワークインタフェースは RHINET/NI と呼ばれる. RHINET/NI はホスト上のソフトウェアオーバヘッドを除外するために、ユーザレベル通信とゼロコピー通信をハードウェアで提供する. また、高い通信性能を実現するために、基本的な通信機能をハードウェアで提供している. ユーザに対してハードウェアで提供する通信処理をプリミティブと呼び、ネットワークインタフェースに対してプリミティブの要求を発行することで通信処理を起動する.

RHINET のネットワークスイッチは RHINET/SW と呼ばれる. RHINET/SW では、ネットワーク上でのパケットの順序性を保証し、かつデッドロックによるパケットの破棄を行わないよう、縮約構造化チャネル法 [28] を採用し、ソフトウェアによる通信保証処理を不要としている. また、スイッチを経由することによる遅延の加算を低く抑えるために、Asynchronous Wormhole Routing[29] を採用している.

#### 2.2.1.1 RHINET-1

RHiNET の最初の実装である RHiNET-1 は、ネットワークインタフェース RHiNET-1/NI、ネットワークスイッチ RHiNET-1/SW、及び 1.33Gbps の転送容量を持つ光リンクで構成される.

RHiNET-1/NI は、PC で標準的に利用されている 32bit/33MHz の PCI バスに接続するネットワー

クインタフェースであり、光インタコネクションモジュール、CPLD (Complex Programmable Logic Device) を用いたコントローラ部、アドレス変換テーブル保存用のメモリなどで構成される.

RHiNET-1/SW は  $0.35\mu m$  プロセスの CMOS エンベデッドアレイによる 1 チップの ASIC スイッチ LSI と大容量の外部 SRAM で構成される. 外部 SRAM はパケットバッファとして用い, チップ内部のメモリをキャッシュとして利用する仮想チャネルキャッシュ方式 [28] を採用している. また, チップ内に  $8\times8$  のクロスバを内蔵し, 光インタコネクションモジュールを 8 組接続可能な構造となっている. フロー制御は Stop-and-Go 方式で行っている.

#### 2.2.1.2 RHINET-2

RHiNET-2 は、多様な形態のネットワークスイッチ、ネットワークインタフェース、及び伝送媒体をサポートしたインターコネクトである。RHiNET-2 は RHiNET-1 と同様にネットワークスイッチ、ネットワークインタフェース、光リンクで構成される.

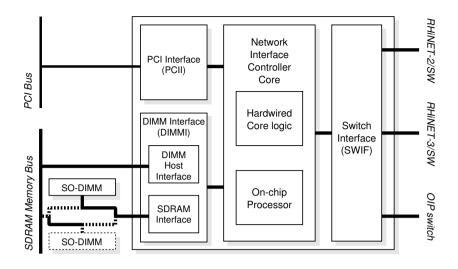

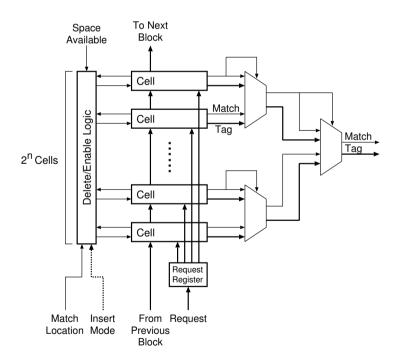

RHiNET-2/NI は、64bit/66MHz の PCI バスに装着するネットワークインタフェースであり、コントローラ部に Martini[30][31][32][33][34] と呼ばれる専用 ASIC を搭載している。さらに、RHiNET-2/SW に接続可能な光インタコネクションモジュールやノート PC 用の SDR SO-DIMM を備える。Martini には RDMA read/write<sup>(注 2)</sup>のプリミティブしか実装されておらず、PUSH/PULL 以外の通信処理や例外処理はオンチッププロセッサやホストでソフトウェア処理するという方針で設計されている。この Martini は DIMMnet-1 のネットワークインタフェースコントローラとしても使用された。Martini のブロック図を図 2.7 に示す。Martini は RHiNET-2 と DIMMnet-1 という、ホストとのインタフェースが異なるインターコネクトをサポートするために PCI インタフェース部と DIMMインタフェース部を持つ。ハードワイヤードロジック部には RDMA 転送を実現するための DMA制御部や、ハードウェアサポートされていない通信の処理や例外処理用のオンチッププロセッサが搭載されている。Switch Interface は RHiNET-2 用のスイッチのほか、RHiNET-3 用のスイッチなど、様々なスイッチとの接続をサポートする。

Martini には、RDMA による転送のほか、PIO による通信機構をサポートし、BOTF (Block On-The-Fly)[35] と AOTF (Atomic On-The-Fly)[36] という少量のデータ転送用の低遅延な通信機構を提供している

RHiNET-2/SW は  $0.18\mu m$  プロセスの CMOS エンベッデッドアレイで構成される 1 チップスイッチである. チップ内部に大容量の SRAM を持ち、外部メモリを必要とせず、さらに、1Gbps に加え 8Gbps の光リンクに対応している. RHiNET-2 には光インタコネクションモジュールを搭載せずに、電気信号 (LVDS) を用いる実装も存在する.

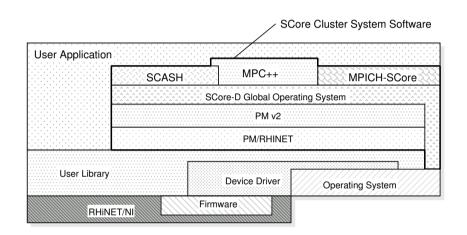

#### 2.2.1.3 RHINET のソフトウェア

RHiNET は、基本通信処理へのソフトウェアの介在を極力減らすことで、高スループットで低レイテンシな通信を実現するインターコネクトである。しかし、ハードウェアで提供されていない通信機能や例外処理、ホスト上でのデバイス管理などにおいてはソフトウェアが必要となる。RHiNET-2システムのソフトウェアレイヤは、個々のノード上に構築される。RHiNET-2システムのソフトウェアレイヤを図 2.8 に示す。

階層の底辺にはハードウェアである RHiNET/NI が位置し, その上にオンチッププロセッサで実

<sup>(</sup>注 2)RDMA write を PUSH, RDMA read を PULL と呼ぶ

図 2.7 Martini のブロック図

図 2.8 RHiNET のソフトウェアレイヤ

行されるファームウェアが位置する. それより上位はホスト PC 上で実行されるソフトウェアレイヤであり, カーネルレベルで実行されるデバイスドライバとユーザレベルで実行されるユーザライブラリが位置している.

ユーザライブラリはデバイスドライバや OS を介することなく RHiNET/NI に直接アクセスし、プリミティブやそのほかの処理を要求することが可能である. メモリ管理機能などの, 通信と直接関わらない処理はユーザライブラリやデバイスドライバから OS の機能を利用して実現する.

ユーザはユーザライブラリを直接用いて並列アプリケーションを記述することができるが、 PM/RHiNET[37] と呼ばれる、SCore システム [38] の通信ライブラリを用いることで、SCore システムを RHiNET 上に実現し、その上で並列アプリケーションを記述することも可能である.

図 2.9 Myrinet-2000 ネットワークインタフェースのブロック図

#### 2.2.2 Myrinet

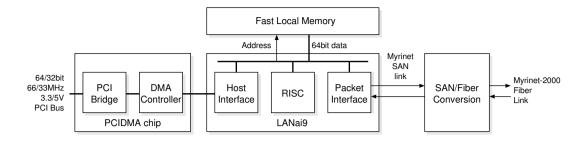

Myrinet[2] は細粒度並列処理に対応した並列計算機である Caltech Mosaic C[39], 及び Mosaic に用いられた USC/ISI ATOMIC LAN [40] の研究成果から生まれたインターコネクトである. 専用のRISC プロセッサを搭載したネットワークインタフェースと, 専用のネットワークスイッチ, 及びそれらを接続するリンクにより構成されている. Myrinet は ANSI で規格化されており, リンクとルーティングの規格は公開されている. 現在, 米 Myricom 社 [41] によって開発, 販売が行われている.

Myrinet のネットワークインタフェースは LANai  $^{(\dot{z}\ 3)}$  と呼ばれるネットワークインタフェースコントローラと大容量の SRAM を搭載する. LANai は内部に 32bit の RISC プロセッサを持ち、ネットワークインタフェース上でのプロトコル処理は RISC プロセッサ上で実行される MCP (Myrinet Control Program) と呼ばれるファームウェアによって実現される. SRAM は通信バッファなどに用いられる. また,LANai 外部の専用コントローラ $^{(\dot{z}\ 4)}$  によって,ホスト PC 上の物理メモリやネットワークとの間での DMA 転送が提供されている. 通信の信頼性と順序性は MCP によって保証される.

LANai は仕様が公開されているため、ユーザがMCPを開発することも可能であり、PM[42][43][44] や BIP[45] などの、MCP を独自に開発することで高性能な通信を実現しようとする研究が数多く見られる。 図 2.9 に第 3 世代の Myrinet である Myrinet-2000 用のネットワークインタフェースの構成を示す。 図の中央には、LANai9[46] と呼ばれるコントローラが位置している。

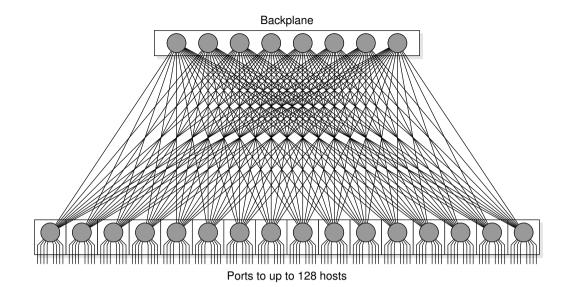

Myrinet のスイッチは、カットスルー方式でパケットのスイッチングを行うクロスバスイッチであり、Stop-and-Go 方式のパケット転送を行う。  $8\times8$  や  $16\times16$  のクロスバスイッチをバックプレーンを介して多段接続し、Fat-Tree や Clos 網と呼ばれるトポロジの結合網を構築してノード間を接続する。  $16\times16$  のクロスバスイッチを組み合せて Fat-Tree を構築し、128 ノードの接続に対応した Myrinet の結合網を図 2.10 に示す。このような結合網上でノード側でソースルーティングによる経路選択を行うことで、トラフィックの分散や経路の冗長化を実現する。

Myrinet は信頼性の高いリンクを用いており、エラー発生率は低いが、さらに CRC (Cyclic Redundancy Check) を用いたエラー検出を提供している.

#### 2.2.2.1 第 1 世代および第 2 世代の Myrinet

1994 年に登場した最初の Myrinet は, Sun Microsystems 社のワークステーションをホストとしてサポートしており, ネットワークインタフェースは SPARC 向けのバスである SBus を介してホ

<sup>(</sup>注 3)最近のものは "Lanai" と表記が変更されている.

<sup>(</sup>注 4)最近の Myrinet のネットワークインタフェースではこれらは LANai に統合されている.

図 2.10 16×16 のクロスバスイッチを多段結合して Fat-Tree を構築した Myrinet の結合網

ストと接続可能であった. リンク速度は 0.64G+0.64Gbps であった.

1990年代後半に登場した第2世代のMyrinetであるMyrinet-1280はリンク速度が1.28G+1.28Gbps に強化された. ネットワークインタフェースには33MHz 動作のLANai (LANai4[47]) と最大1MByte の SRAM が搭載され、SBus に加えて新たに32bit/33MHzのPCI バスへの対応が行われた. LANai は改良を加えられ、LANai5[48] からは外部へのバスが64bit に拡張された. また、LANai7[49] は66MHzで動作し、64bit/66MHz PCI バス対応のネットワークインタフェースも登場した.

この頃の Myrinet のリンク媒体には銅線が用いられており. SAN モードと呼ばれる接続方式では最大 3m, LAN モードと呼ばれる接続でも最大 10m と, Ethernet などの LAN と比べてリンク長に厳しい制限が存在していた.

#### 2.2.2.2 Myrinet-2000

2000 年頃に登場した第 3 世代の Myrinet は Myrinet-2000 と呼ばれ, リンク速度が 2.0G+2.0Gbps に向上した. 当初はネットワークインタフェースとして 64bit/66MHz PCI バスに対応したもの (最大 200MHz 動作の LANai (LANai9[46]) を搭載) が提供されていたが, 後に 64bit/133MHz の PCI-X バスに接続可能なもの (最大 333MHz 動作の Lanai (LanaiX[50]) を搭載) が登場している. PCI-X バスの転送能力と比較してリンク速度は低いが, この問題を回避するためにネットワークインタフェース上のポート数を 2 ポートに増やして, ノード間のデータ転送速度の強化を図ったデュアルポート形式のネットワークインタフェースも提供されている.

ネットワークスイッチには XBar16 や XBar32 と呼ばれるスイッチチップが用いられ, 最大 32 ポートのクロスバスイッチが提供されている.

リンクの媒体は光ファイバ (50/125 マルチモードファイバ) が標準となっており, 最大で 200m まで延長可能となっている. 光ファイバ以外にも, 銅線によるシリアル接続である HSSDC (High Speed Serial Data Connector, 最大 10m), 及び内部に全二重のリンクを 2 つ備える Myrinet-SAN ケーブル (最大 3m) と呼ばれるマイクロリボンケーブルのそれぞれに対応するネットワークインタフェース

が提供されている.

#### 2.2.2.3 Myri-10G

Myri-10G は 10GbE (10Gigabit Ethernet) との相互運用が可能な Myricom 社による最新のインターコネクトである. IEEE 802.3ak や IEEE 802.3ae といった 10GbE と同じ物理層の規格を採用しており、スイッチやネットワークインタフェースのリンクの媒体には 10GBASE-CX4 規格の銅線や 10GBASE-R 系列の光ファイバの利用が可能である. Myri-10G のリンク速度は 10G+10Gbps である. それに対してネットワークインタフェースは PCI Express x8 を介した接続に対応しているため、ホストとの間は 16G+16Gbps の全二重接続となり、リンクに対して十分なデータ転送性能を提供可能な構成となっている.

Myri-10G のネットワークインタフェースは, 300MHz 以上のクロックで動作する Lanai (Lanai Z8E) を搭載し, 従来の Myrinet と同様にソフトウェアを用いてプロトコル処理を行う. Lanai 上のファームウェアを用いて, データリンクレベルで Myrinet と 10GbE の両方のプロトコルに対応することができるため, Myri-10G のネットワークインタフェースは 10GbE のネットワークインタフェースとしても利用可能である.

#### 2.2.2.4 Myrinet のソフトウェア

Myrinet 向けのソフトウェア環境については、Myricom 社により低レベル通信ライブラリである GM が提供されており、GM を利用した MPI や TCP/IP の実装が用意されている。 また、MX (Myrinet eXpress) と呼ばれる、より低遅延な通信を提供する通信ライブラリが用意されている [51].

#### 2.2.3 Quadrics Network

QsNET (Quadrics NETwork)[3][52][53] は、Compaq と Los Alamos 国立研究所の共同プロジェクトである 30 TeraOps ASCI Q-machine と呼ばれる SMP クラスタ用に開発されたインターコネクトである. 現在は Quadrics 社 [54] によって開発・販売が行われている. QsNET はプログラマブルなネットワークインタフェースと高スループットかつ低レイテンシなネットワークスイッチで構成される.

QsNETのネットワークインタフェースには Elan と呼ばれるプログラマブルな ASIC が搭載される. Elan は内部に DMA 要求やパケット処理などの通信処理を専門に行うプロセッサと, MPI などの上位の通信プロトコルを実装するのに用いるプロセッサを内蔵する. また, Elan は MMU を内蔵しており, Elan 内部の処理で用いられる仮想アドレスを, ホスト上のメモリやネットワークインタフェース上の外部メモリの物理アドレスに高速に変換できるようになっている. さらに, ネットワークインタフェース上のメモリをユーザのメモリ空間にマップすることも可能であり, これにより, Elan からホスト上のメモリとネットワークインタフェース上のメモリに対して透過的にアクセスすることが可能になる. そのほか, Elan はプロセッサ用のキャッシュやリンク接続用のロジックなどを内蔵している.

QsNET のスイッチには Elite と呼ばれる ASIC が搭載されている. Elite は 4-array Fat-Tree トポロジを基本とするフルクロスバスイッチである. Elite はソースルーティングに対応し, パケットの先頭についたタグの並びに応じてルーティングを行う. タグは任意の出力ポートの集合を指すこと

ができ、これを利用したハードウェアマルチキャストがサポートされている。パケットは Wormhole 方式で転送され、送信元ノードと宛先ノードの間の経路は、宛先ノードがパケットを受け取ってから送信元ノードに確認応答 (Ack) を返すまで維持される.

さらに、複数レイヤで構成される通信ライブラリを提供しており、これらハードウェアとソフトウェアを組み合わせて、安全で効率的にアクセス可能なグローバル仮想アドレス空間を構築する. OsNET はリンクレベルでエラー検出と再送を行うことで、高い信頼性を実現している.

#### 2.2.3.1 QsNET のプロトタイプ

QsNET は Meiko Scientific 社によって開発された MPP (Massively Parallel Processing) である Meiko CS-2[55] に用いられたインターコネクトが元になっている. CS-2 は SPARC (SuperSPARC または hyperSPARC) とメモリ, 通信用 Co-processor を 1PE とするシステムであり, この通信用の Co-processor は Elan と名付けられた. Elan は SPARC 向けのバスである MBus 経由でアクセスされ, Elan のインターコネクト側のリンク速度は 0.4+0.4Gbps であった.

インターコネクトには Fat-Tree のトポロジが用いられ、ネットワークスイッチに用いられた 8×8 のクロスバスイッチは Elite と呼ばれた. Elite はマルチキャストに対応していた.

#### 2.2.3.2 **QsNET**

QsNET はネットワークインタフェースコントローラに Elan3 を搭載した 64bit/66MHz PCI バスに装着するネットワークインタフェースと, Elite3 を搭載したネットワークスイッチから構成される.

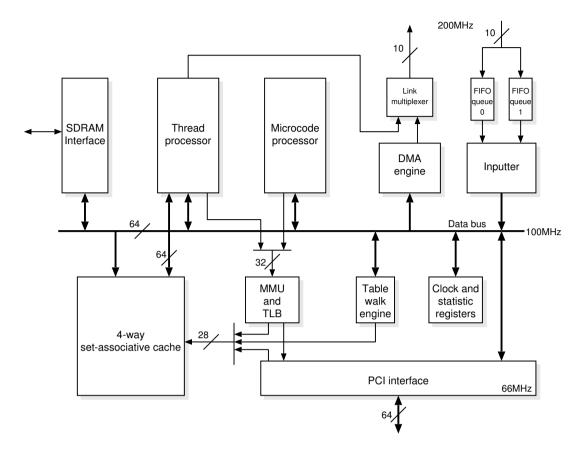

Elan3 は 100MHz で動作する通信処理専用プロセッサ (マイクロコードプロセッサ) と, 上位プロトコル処理用プロセッサ (スレッドプロセッサ) を持つ. どちらも 32bit プロセッサであり, スレッドプロセッサは 8KByte の 4-way セットアソシアティブキャッシュを持つほか, 通信処理やスケジューリングを支援する拡張命令を備えている. また, Elan3 は 32bit の仮想アドレスを 28bit のローカル SDRAM アドレス, または 48bit のホスト物理アドレスへ変換する MMU, 送受信で各々2 つの仮想チャネルを持つ Link ロジックなどを搭載している. Elan3 のブロック図を図 2.11 に示す.

Elite3 は 2 つの仮想チャネルを備えた 8 つの双方向リンクを持つ 16×8 のフルクロスバスイッチ (入力ポートはチャネルごとに独立) であり、3.2G+3.2Gbps のリンク速度に対応する. また、CRC によるパケットエラー検出やリカバリにより、信頼性の高い通信を実現する.

#### 2.2.3.3 **QsNET II**

QsNET II[56][57] はネットワークインタフェースコントローラに Elan4 を搭載した 64bit/133MHz PCI-X バスに装着するネットワークインタフェースと, Elite4 を搭載したネットワークスイッチから構成される.

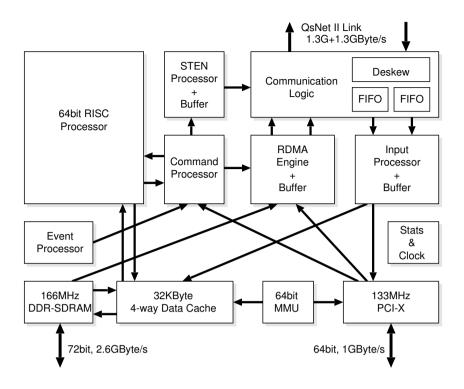

Elan4 は Elan3 と比べて、内部プロセッサの 64bit 化、並びに 64bit の仮想アドレススペースのサポート、短パケット処理専用ユニット STEN (Small Transaction ENgine) の搭載といった変更が加えられている。 また、Elan4 は Elan3 同様、スレッドプロセッサ (図 2.12 の 64bit RISC processor) を持つ一方、マイクロコードプロセッサを持たず、複数のプロセッサを搭載することにより、これに相当する機能を実現している。 図 2.12 に Elan4 のブロック図を示す。

図 2.11 Elan3 のブロック図

Elite4 は 13G+13Gbps (実効データ転送速度は 10.6G+10.6Gbps) のリンク速度, 及び最大 100m のリンク長に対応する.

#### 2.2.3.4 QsNET のソフトウェア

QsNET では、Quadrics 社によって Elanlib[58] と呼ばれる独自のソフトウェアライブラリが提供されており、その上で動作する MPI-2 などの標準的な並列プログラミング環境が用意されている . また、Quadrics 社よりデバイスドライバや qsnetlibs と呼ばれるユーザライブラリなどがオープンソースで提供されているため、ユーザが Elan 上のプログラムを独自に開発することも可能となっている.

#### 2.2.3.5 **QsTenG**

QsTenG は Quadrics 社が提供する 10GbE のネットワーク環境である [59]. 並列分散処理のみならず、データセンターなどでの利用を視野に入れている. 提供されているのはネットワークスイッチのみであり、ネットワークインタフェースやケーブルは汎用の 10GbE の製品を使用する. ネットワークスイッチにはカットスルー方式を採用しており、スイッチ通過遅延が 200ns と低く抑えられている.

図 2.12 Elan4 のブロック図

#### 2.2.4 InfiniBand

InfiniBand[4] は、IBTA (InfiniBand Trade Association)[60] によって策定されたインターコネクトアーキテクチャである。InfiniBand はサーバ I/O やサーバ間の通信に RAS (Reliability, Availability, Scalability) を提供することを目的に開発されており、従来の I/O に用いられていたバスアーキテクチャの性能面の問題を解決するために、スイッチベースアーキテクチャとなっている。最初の規格として、InfiniBand Architecture Specification Release 1.0[61] が 2000 年に策定されている。

当初、InfiniBand は PCI バスなどの汎用 I/O バスに取って代わる内部インターコネクトと、外部との接続に用いるクラスタリングという、異なる分野を統合するインターコネクトとして開発が始められた。しかし、Intel によって PCI バスの後継となるチップ間のインターコネクト規格として PCI-Express が提案され、汎用 PC において普及したため、内部インターコネクトとしての必要性は薄れ、現在はクラスタリングを主なターゲットとしたネットワーク規格となっている。

このように、InfiniBand は規格が標準化されていることから様々なベンダから製品が供給されているため、Myrinet や QsNET よりも量産効果による価格の低下が期待できる.このことから,DIMMnet-2 においてはネットワークインタフェース以外のネットワークコンポーネントに InfiniBand を採用している.

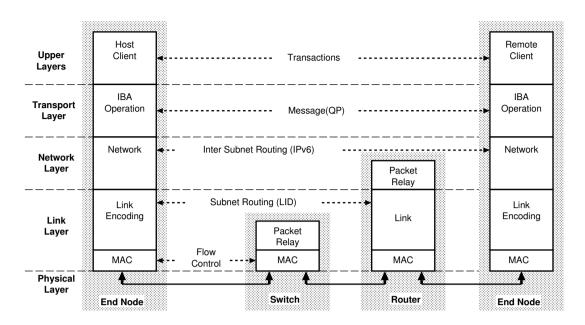

#### 2.2.4.1 InfiniBand のプロトコル

InfiniBand では、物理層、データリンク層、ネットワーク層、及びトランスポート層の各通信層においてプロトコルが定められている(図 2.13).

• 物理層 (Physical Layer)

図 2.13 InfiniBand のプロトコル階層

InfiniBand の物理層では、片方向2本のシリアル差動信号方式で伝送を行う双方向の4本の信号線を基本構成(1X)とする. 1X は片方向2.5Gbpsのデータレートを実現するが、8B10Bエンコーディングを用いているため、実効データ転送レートは片方向当たり2Gbpsとなる.物理層のメディアとしては、プリント基板、銅線、及びファイバケーブルが使用可能である.

この 1X の信号線の対を 4 本束ねた 4X や 12 本束ねた 12X が規格として定義されており、それぞれ、10Gbps、30Gbps のデータ転送速度を提供する。2004 年に策定された InfiniBand Architecture Specification Release 1.2[62] では DDR と QDR の動作モードが新たに追加され、最大で 120Gbps のデータ転送速度が規定されている。

#### • データリンク層 (Link Layer)

InfiniBand のデータリンクレベルのパケットには、通常のデータ転送に用いるデータパケットと、リンクの管理などに用いる管理パケットが存在する。データパケットのサイズは最大4KByte である.

InfiniBand において、スイッチで構成されるネットワークをサブネットワークと呼ぶ. サブネットワーク内のパケットスイッチングはリンク層で処理される. 16bit の LID (Local ID) が Subnet Manager (後述) によって各デバイスに割り付けられ、LID を用いてスイッチングする.

各物理リンクは、VL (Virtual Lane) と呼ばれる論理的な通信路を持っており、15本のデータ用 VL (VL0~VL14) と 1本の管理用 VL (VL15) が存在する. 数字が大きいほど優先度が高く設定されている. QoS (Quarity of Service) を保証するために、SL (Service Level) が定義されており、スイッチやルータは、SL と VL の対応を保持することで、適切な QoS を提供することが可能となる.

VL ごとに受信側が送信側に受信可能なデータ量をクレジットという形で通知することでフロー制御を実現する, クレジットベースのフローコントロールが Point-to-Point で用いられる.

データリンク層の CRC には、VCRC (Variant CRC) と ICRC (Invariant CRC) の 2 つの CRC

が存在する. VCRC がホップ間でリンクレベルのデータの整合性を保証し, ICRC が end-to-end のデータ整合性を保証する. Ethernet などの CRC が一つしかないプロトコルでは, デバイス で発生したエラーも含めて CRC が再計算されてしまうのに対し, InfiniBand では ICRC により常にエラーを検出できる.

スイッチではルーティングテーブルを用いたルーティングを行う. スイッチにおいてマルチキャストを行うことも可能である.

#### • ネットワーク層 (Network Layer)

ネットワーク層はサブネットワーク間のルーティングを行う. サブネットワーク間の通信には InfiniBand ルータが用いられ, IPv6 (Internet Protocol version 6) で表記された送信元と送信先の情報で通信を行う.

#### • トランスポート層 (Transport Layer)

トランスポート層では、Send Queue と Receive Queue から構成される QP (Queue Pair) という送受信用のキューを用いた通信が提供される。 QP 間でパケットシーケンス番号を用いた Ack/Nack プロトコルにより、ノード間のパケット到達保証を行う.

QPを用いた通信では、コネクション型の通信とデータグラム型の通信が規定されており、それぞれに対して、パケットの到達保証と順序保証が行われる信頼性のあるモード (RC: Reliable Connection, RD: Reliable Datagram) と不正なパケットの破棄のみが行われ、再送処理が行われない信頼性のないモード (UC: Unreliable Connection, UD: Unreliable Datagram) が利用可能である.

また、QPを用いないデータグラム型の通信モード (Raw Datagram) も提供されている.

#### 2.2.4.2 InfiniBand の構成要素

InfiniBand は CA (Channel Adapter) と呼ばれるホストインタフェース, スイッチ, ルータの各種 ハードウェアとサブネットワークの管理を行う Subnet Manager から構成される.

CA はノード間接続に用いられる HCA (Host Channel Adapter) と、ストレージなどの I/O デバイスとの接続に用いられる TCA (Target Channel Adapter) の 2 種類が存在する. スイッチは LID を用いてサブネットワーク内のパケットの転送を行い、ルータはサブネットワーク間のパケットのルーティングを行う.

CA を搭載したノードとスイッチから構成されるサブネットワーク内には Subnet Manager が少なくとも 1 つ存在する必要がある. Subnet Manager はスイッチやルータの管理, リンクの up/down 時の再設定を行う. そのため, すべての CA, 及びスイッチには Subnet Manager と通信するための SMA (Subnet Manager Agent) が実装されている必要がある. Subnet Manager はサブネットワーク内のどのデバイス上にも存在することが可能である.

#### 2.2.4.3 高性能通信へのアプローチ

InfiniBand は様々なベンダが製品をリリースしており、代表的なベンダとして、Mellanox 社 [63] が挙げられる. Mellanox 社の HCA には InfiniHost という高性能なネットワークインタフェースコントローラが搭載されており、通信処理をネットワークインタフェースコントローラ上で行うことでホストプロセッサの負荷を低減している.

これに対し、QLogic 社 [64] の InfiniPath[65] (注 5) ではネットワークインタフェースコントローラは最低限のデータ送受信の機能のみを提供し、それ以外の複雑な処理はすべてホストプロセッサで実行することで、通信性能を向上させるアプローチをとっている。これは、

- 1. ネットワークインタフェースコントローラはホストプロセッサに比べて動作周波数が低く、 複雑な処理をネットワークインタフェースコントローラで実行した場合に通信性能が低下す る可能性があること

- 2. 今後, ホストプロセッサがマルチコア化し, ホストプロセッサの演算能力がインターコネクトの性能に比べて大幅に高くなると予想されること

#### が背景として挙げられる.

MPI レベルの最小通信レイテンシを比較すると、Mellanox 社の HCA が約  $4.0\mu$ s なのに対し、InfiniPath の通信性能は  $1.29\mu$ s と通信レイテンシが低く抑えられている [66][67]. しかし、InfiniPath のアプローチでは、ホストプロセッサのキャッシュが通信処理で使用され、アプリケーションの性能に影響を与える可能性があるため、一概に InfiniPath のアプローチが良いとは言い切れない.

#### 2.2.4.4 InfiniBand のソフトウェア

InfiniBand の仕様では VIA (Virtual Interface Architecture)[68] を拡張した verb と呼ばれる, CA の提供すべき機能のみが定められている. 具体的な API の定義は各ベンダに委ねられており, Mellanox 社による VAPI[69] などが存在する. VAPI はメッセージ通信と RMA (Remote Memory Access) 型の通信の両方をサポートし, InfiniBand で規定されているトランスポートサービスのうち RC と UD を提供している. また, オハイオ州立大学によって MVAPICH[70] と呼ばれる, VAPI 上で動作する MPI が実装されている.

#### 2.2.5 10Gigabit Ethernet

近年,並列分散処理環境用インターコネクトにおいて, Myri-10G や InfiniBand のように物理的に 10GbE と互換性を持ち, Ethernet としても用いることが可能なインターコネクトが登場している. また, 10GbE のスループットが PC クラスタ向けインターコネクトに匹敵しており, 量産効果により導入コストが下がっていくことが確実であることから, 今後, PC クラスタへの導入が進むことが 期待される.

10GbE のネットワークインタフェースは既に多くのベンダからリリースされており, Intel 社をはじめ, Chelsio Communications 社 [71], Neterion 社 [72], NetEffect 社 [73], NetXen 社 [74], Tehuti Networks 社 [75], LeWiz Communications 社 [76] などがベンダとして挙げられる.

これらのネットワークインタフェースはいずれも TCP の処理の一部, またはすべてをネットワークインタフェースコントローラ上で実行でき, TCP/IP 使用時のホストオーバヘッドの低減が図られている. これは, ネットワークの速度が 10Gbps クラスになると, ネットワークインタフェースコントローラのサポートがない場合, 通信処理だけでホストプロセッサの処理能力の大半が消費されてしまうためである. また, これらのネットワークインタフェースのうち, Chelsio Communications社, NetEffect社, NetXen社の製品では, iSCSI のアクセラレーションや, iWARP 準拠の RDMA の機

<sup>(</sup>注 5)もともと、InfiniPath は PathScale 社が開発, 販売していたが、2006 年に QLogic 社に買収された

図 2.14 スループットの上昇曲線

能を提供している. iWARP は RDMA Consortium[77] によって策定された, TCP/IP 上での RDMA の利用 (RDMA over TCP/IP) に関する規格である.

これらの機能により、10GbE の性能はスループットの面においては Myri-10G や InfiniBand に匹敵する性能を達成している。また、これまで Ethernet のネットワークスイッチは Store and Forward 方式のものが大多数であり、HPC 用途で用いるにはレイテンシが大きかったが、QsTenG のようにカットスルー方式のネットワークスイッチがベンダより提供されるようになってきたため、レイテンシも低く抑えることが可能になっていくと考えられる。

#### 2.2.6 まとめ

本節においては、並列分散処理環境向けに開発されたインターコネクトについてまとめた。

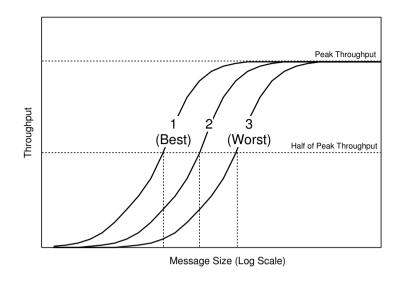

最後にこれらのインターコネクトの性能の比較を表 2.2 に示す. 表 2.2 内に示した通信性能は RHiNET-2, Myrinet-2000, 及び InfiniPath を除き, 参考とした文献の片方向のスループットのグラフから読み取ったものである. また, 括弧で囲まれているものは, MPI レベルの通信性能である. half of peak throughput は片方向通信時に最大スループットの半分のスループットが得られるデータサイズを示しており, インターコネクトのレイテンシの小ささを示す指標の 1 つである [66].

一般に、インターコネクトのスループットは、図 2.14 のように、あるデータサイズから急激にスループットが上昇し、ある一定値に落ち着くというグラフを描く. これは、転送するデータサイズが小さい間は通信のセットアップに要するレイテンシが通信処理全体のレイテンシに大きな影響を与えるためである. 通信のセットアップに要するレイテンシは転送するデータサイズに依存せず一定である場合が多く、転送するデータサイズが大きくなるに従って、このレイテンシの影響は小さくなる. よって、このレイテンシが小さいほど、スループットが上昇し始めるのが早くなる. 図 2.14 では、1~3 のグラフはすべて最大スループットは同じであるが、1 のグラフが最も低レイテンシであると言える.

half of peak throughput の値が大きいと、スループットの最大性能が得られるようになる転送データサイズが大きいということになり、そのようなサイズのメッセージを転送しないアプリケーション

|             | 我 2:1 お送し100万プピープライスと間数 |          |          |     |  |

|-------------|-------------------------|----------|----------|-----|--|

| Application | <2K                     | 2K - 16K | 16K - 1M | >1M |  |

| IS          | 14                      | 11       | 0        | 11  |  |

| CG          | 16113                   | 0        | 11856    | 0   |  |

| MG          | 1607                    | 630      | 3702     | 0   |  |

| LU          | 100021                  | 0        | 1008     | 0   |  |

| FT          | 24                      | 0        | 0        | 22  |  |

| SP          | 9                       | 0        | 9636     | 0   |  |

| BT          | 9                       | 0        | 4836     | 0   |  |

| Sweep3D-50  | 19236                   | 0        | 0        | 0   |  |

| Sweep3D-150 | 28836                   | 28800    | 0        | 0   |  |

|             |                         |          |          |     |  |

表 2.1 転送されるメッセージサイズと個数

においては、インターコネクトの性能の恩恵を受けられない。表 2.1 は NAS Parallel Benchmarks[78] の Class B, 及び ASCI Sweep3D ベンチマーク [79] を 8 ノード (16CPU) の PC クラスタで動かした際のメッセージサイズごとのメッセージの転送回数を示したものである [80]。これらのベンチマークのうち、CG、MG、LU、及び Sweep3D においてはメッセージサイズが 2KByte 未満のメッセージが多数転送されており、このようなアプリケーションにおいては、最大スループットが高いがレイテンシが大きいインターコネクトよりも、多少スループットが劣っても低レイテンシなインターコネクトの方が良い結果を得る可能性が高いと言える。

表 2.2 に示したインターコネクトのうち、PCI、及び PCI-X に接続されながらも、専用の低遅延通信機構を持つ RHiNET-2、及び QsNET II のレイテンシが PCI-Express に接続されるインターコネクトよりも低い値を示している。コントローラの動作周波数が 300MHz を超える Myrinet-2000 よりも 66MHz の RHiNET-2 の方がレイテンシが小さいことから、通信処理をハードワイヤードで実現する方がレイテンシを小さく抑えられると言える。 基本通信処理がハードワイヤードで実現されている割には InfiniBand (Mellanox 製) のレイテンシが大きいが、これは InfiniBand のプロトコル処理がほかのインターコネクトに比べて複雑であることが原因と考えられる。 また、PCI バスやPCI-Express よりも低レイテンシな I/O バスに接続される InfiniPath が最も低いレイテンシを示していることから、I/O バスのレイテンシが性能に与える影響は大きいと思われる。

一方、スループットは接続される I/O バスの最大スループットに近い値が出ており、また、I/O バスの世代が新しくなるにつれ、それに従った性能が得られていると言える。 さらに、片方向の I/O バスである PCI バスや PCI-X バスから双方向の I/O バスである PCI-Express や HyperTransport に置き換わったことが大きな影響を与えている。

### 2.3 メッセージ通信を支援する通信機構

近年、PC クラスタ向けインターコネクトにおいて、ネットワークインタフェースに搭載されているコントローラを利用して、MPI に代表されるメッセージ通信を支援する機構を搭載する研究が行われている。これは、PC クラスタにおいては並列アプリケーションを記述する際に、メッセージ通信ライブラリが多く用いられていることを背景としている。メッセージ通信では、メッセージの受信処理時に受信関数で指定したパラメータに一致するメッセージを探索するなどの処理が行われ

る. そのため、基本通信性能が高いインターコネクトであっても、インターコネクト側でメッセージ通信を支援する機能がない場合、メッセージ通信レベルの通信レイテンシやホストプロセッサのオーバヘッドが高くなる. その結果、このようなアプリケーションにおいては基本通信性能から期待されるほどの性能が得られないことになる.

本節では受信側のネットワークインタフェースコントローラがメッセージの受信先アドレスを 指定する方式のメッセージ受信機構,及びネットワークインタフェースコントローラが MPI のメッ セージ受信処理をホストプロセッサに代わって実行する手法について述べる. また, それらの手法 が抱えている問題点を明らかにする.

### 2.3.1 受信側がメッセージの受信先アドレスを指定する受信機構

PC クラスタに代表される分散メモリ型の並列システムにおいては、各ノードで動作するプロセス間の通信にメッセージ通信が用いられる。メッセージ通信において各プロセスはメッセージを明示的に送信、及び受信することで並列処理を実現する。メッセージの送受信において、RDMA をサポートしないインターコネクトの場合、一度カーネルのバッファにメッセージをコピーするなどの操作により、メッセージの送受信を実現する。しかしながら、カーネルを介した場合、受信のオーバヘッド、レイテンシは RDMA より増大する。

一方、ネットワークインタフェースが RDMA をサポートするインターコネクトでは、受信先のアドレスを事前に通知し合うなどの手段によって送信側が受信先のアドレスを知る必要があるものの、受信側が明示的な受信処理を行う必要がなく、受信側ホストのオーバヘッドが小さいという利点がある。そのため、RDMA を用いてメッセージ通信を実現することで高い性能を得ることができる。しかしながら、複数プロセスから単一の受信領域に対して RDMA を行う場合、各プロセスは独立に RDMA でメッセージを送信してしまうため、受信メッセージが書き潰されてしまうことが起こり得る。これを防ぐために、通信ごとに送信側と受信側で転送サイズやメッセージ転送領域を通知し合うか、受信側で送信プロセスごとに受信領域を分けるといった対策をとる必要がある。前者の場合、通信レイテンシの増大を招くことになり、後者の場合、通信プロセス数が増大した際のスケーラビリティに乏しいという問題が存在する上に、メッセージを到着した順番に読み出すことが難しくなる。

このような背景から DIMMnet-1 (3.1 節) におけるリモート間接書き込み [87][88] や, RHiNET-2 における VPUSH[89] のような "受信側のネットワークインタフェースコントローラがメッセージ の受信先アドレスを指定する" というメッセージ受信の手法が提案された. これらは共に, ネットワークインタフェースコントローラである Martini に搭載されたオンチッププロセッサを用いたソフトウェア処理とハードワイヤードで実装された通信機構が協調処理を行うことによって実現されている.

DIMMnet-1 のリモート間接書き込みでは、送信側で受信側のメッセージ受信先アドレスが格納された領域を指すポインタ値をセットし、受信側にメッセージを送信する。 受信側では、そのポインタ値が指す領域に格納されたメッセージ受信先のアドレスを取得し、そのアドレスに従ってメッセージを格納する。 受信先のアドレスの取得、フロー制御、ACK パケットの処理などをすべてオンチッププロセッサで実行していたが、オンチッププロセッサが例外処理用の簡素なものであり、性能が高くなかったため、RDMA と比較すると大幅に性能が低下していた。

RHiNET-2 で実装された VPUSH では、受信したメッセージのアドレス値の変更、及び受信領域のアドレス管理のみをオンチッププロセッサで行い、パケットのヘッダ解析や主記憶への DMA は

ハードワイヤード部で行う. VPUSH は RDMA の最大スループットの 38%程度の性能を示したが、 やはりオンチッププロセッサの性能から、 RDMA と比べてスループットの低下、 受信側のレイテンシの増加が見られていた [30][89]. VPUSH ではパケット長によらず、 オンチッププロセッサの処理時間が  $6.6\mu$ s で一定である. この値はデータサイズが 2048Byte のパケット受信の処理時間の約 60%に相当する. 文献 [89] によると、 データサイズが 2048Byte 時の VPUSH のスループットが 180.3MByte/s であり、 仮にこのソフトウェアオーバヘッドが 0 になった場合は処理時間が約 40%程度になることから、 スループットは約 450MByte/s に到達すると予測される. 実際にはソフトウェアの処理と同等の機能を持つハードウェアによるオーバヘッドが加わり、 若干低い値になると考えられるが、 この値は RHiNET-2 の最大スループットに匹敵する値である.

# 2.3.2 ネットワークインタフェースコントローラによる MPI のメッセージ受信処理の高 速化

MPIではメッセージ受信の際に用いるメッセージキューとして posted receive queue と unexpected message queue の 2 つのキューを用いて、メッセージの受信処理を行う. posted receive queue は受信要求がメッセージの到着前に発行された際に、その要求をバッファリングするためのものであり、unexpected message queue はメッセージの到着が対応する受信要求より先であった場合に、受信データをバッファリングするためのものである.

メッセージを受信した際の処理の流れを以下に示す.

- 1. posted receive queue を探索し, そのメッセージに対応する受信要求が存在するかどうかを調べる.

- 2. 対応する受信要求が存在する場合には、その要求に対するメッセージとして受信側のプロセスに渡され、posted receive queue から受信要求が削除される.

- 3. 対応する受信要求が存在しない場合には、受信したメッセージを unexpected message queue に格納する.

受信要求が発行された場合には,

- 1. unexpected message queue を探索し, 対応する受信メッセージが既に受信されているかどうかを調べる.

- 2. 既に受信されている場合はそのメッセージが受信側のプロセスに渡される.

- 3. 受信されていない場合は、その要求が posted receive queue に格納される.

#### という流れで処理が行われる.

このように、MPI においてはメッセージの受信の際にキューの探索処理が行われるが、アプリケーションによってはキューの探索範囲が大きくなり、その結果、メッセージの受信処理に要するレイテンシが増加するという問題がある [90].

そのため、これらのキューの探索処理をネットワークインタフェースコントローラで行うことでホスト側の負荷の軽減、及び探索処理の高速化を図る研究が数多く行われている。 Myrinet の MX や QsNET の Tports[54] ではマッチングのための API が用意されている。 また、MX を利用した MPICH[91] である MPICH-MX が Myricom 社より提供されている。 これらはプログラマブルなネットワークインタフェースコントローラを利用し、ソフトウェアで実行される。

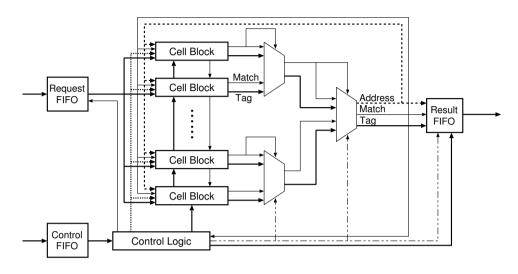

それに対し、文献 [92] では、ALPU (Associative List Processing Unit) という posted receive queue と unexpected message queue の探索処理を行うハードウェアを提案している (図 2.15). ALPU は複数の Cell Block と呼ばれるロジック、結果を出力するためのマルチプレクサ、及び制御ロジックから構成される. Cell Block は  $2^n$  個の Cell から構成される (図 2.16). Cell は単一のマッチング情報の比較を行うユニットである. そのため、ALPU 全体で Cell の個数分のマッチング情報を保持することができる. Cell の個数以内のマッチングにおいては大幅なレイテンシの削減が可能であるが、Cell の個数以上のマッチング情報からマッチングを行う場合には性能が改善しないという問題がある.

文献 [92] では Virtex-II Pro XC2VP100[93] を対象デバイスとしてハードウェア量を評価している. posted receive queue と unexpected message queue に対してそれぞれ Cell の個数が 256 個の ALPU を設けた場合に、総スライス数の約 62.0%を占めており、ハードウェア量が極めて大きいと言える. さらに、ハードウェア量は Cell の個数にほぼ比例するため、スケーラビリティに乏しい.

### 2.3.3 まとめ

リモート間接書き込み、VPUSH はいずれもネットワークインタフェースコントローラの性能が低かったために、高い性能が得られなかった。しかし、VPUSH ではソフトウェア処理を極力少なくすることでリモート間接書き込みよりも高い性能を示していたことから、ハードワイヤードで通信処理を実現するアプローチは性能面で有効であると言える。

Tports や MX におけるマッチング処理のネットワークインタフェースコントローラへのオフローディングはホストプロセッサの負荷を軽減するという点では有効であるが、ホストプロセッサの性能に比べてネットワークインタフェースコントローラの性能は低いため、今後、マルチコア化などによりホストプロセッサとの性能差が広がると、ネットワークインタフェースコントローラがシステムのボトルネックになりうる。また、ALPU のように、マッチング処理をハードワイヤードで実現した場合、ソフトウェアで実現するよりも高い性能が得られると考えられるが、ネットワークインタフェースコントローラのハードウェア量が増大するため、性能とのトレードオフを考える必要がある。さらに、これらの手法はマッチング処理時のキューの探索範囲を削減する手法ではないため、文献 [90] で挙げられている問題を本質的には解決していない。

7章では、メッセージ通信を支援する通信機構である IPUSH と LHS について述べる。これらの通信機構は"ホストプロセッサが効率良く処理できるようにするためのメッセージ受信機構"であり、ホストプロセッサとハードワイヤードによる通信機構の協調処理を行うというアプローチを採っている。 どちらの機構もキューの探索範囲を削減することができるため、本節で述べた手法の問題点を解決可能である。

表 2.2 各インターコネクトの比較

| インターコネクト                | RHiNET-2[34]     | Myrinet-2000[81] | QsNET II[82]  | InfiniBand[83] |

|-------------------------|------------------|------------------|---------------|----------------|

| ネットワークインタフェース           | RHiNET-2/NI      | M3F2-PCIXE       | QM500         | InfiniHost     |

| コントローラ                  | Martini          | LANai-2XP        | Elan4         | MT23108        |

| ベンダ                     | original         | Myricom          | Quadrics      | Mellanox       |

| 基本通信処理                  | Hardware         | Firmware         | Hardware      | Hardware       |

| コアクロック                  | 66MHz            | 333MHz           | N/A           | N/A            |

| ホストインタフェース              | PCI              | PCI-X            | PCI-X         | PCI-X          |

|                         | 64bit/66MHz      | 64bit/133MHz     | 64bit/133MHz  | 64bit/133MHz   |

| リンク性能                   | 600MByte/s×2     | 250MByte/s×2×2   | 1.06GByte/s×2 | 1GByte/s×2     |

| (実効データ転送速度)             |                  |                  |               | (4X)           |

| パケット転送方式                | VCT              | VCT              | Wormhole      | VCT            |

| トポロジ                    | Any              | Any              | Fat Tree      | Any            |

| ホストプロセッサ                | Pentium III      | Opteron          | Itanium2      | Xeon           |

|                         | 933MHz×2         | 1.8GHz×2         | N/A           | 3.4GHz×2       |

| チップセット                  | ServerWorks      | AMD              | Intel         | N/A            |

|                         | ServerSet III LE | AMD-8131         | E8870         |                |

| ファームウェア                 |                  | MX-2G 1.0        |               |                |

| 接続方式                    | back-to-back     | 1 Myrinet switch | N/A           | InfiniScale    |

|                         |                  | $(0.5\mu s)$     |               |                |

| レイテンシ                   | $1.74 \mu s$     | 2.6μs            | 1.6μs         | 4.8μs          |

| スループット (片方向)            | 444MByte/s       | 495MByte/s       | 911MByte/s    | 781MByte/s     |

| half of peak throughput | 1KByte           | 300Byte          | 4K - 8KByte   | 1K - 2KByte    |

| スループット (双方向)            | 470MByte/s       | 912MByte/s       | 900MByte/s    | 946MByte/s     |

| インターコネクト                | InfiniBand[83]    | InfiniBand [67] | Myri-10G[84]   | 10GbE[85][86]   |

|-------------------------|-------------------|-----------------|----------------|-----------------|

| ネットワークインタフェース           | InfiniHost III Ex | InfiniPath HTX  | 10G-PCIE-8A-C  | T110            |

| コントローラ                  | MT25208           | N/A             | Lanai Z8E      | N/A             |

| ベンダ                     | Mellanox          | QLogic          | Myricom        | Chelsio         |

| 基本通信処理                  | Hardware          | Hardware        | Firmware       | Hardware        |

| コアクロック                  | N/A               | N/A             | 300MHz ~       | N/A             |

| ホストインタフェース              | PCI-Express       | HyperTransport  | PCI Express    | PCI-X           |

|                         | 8x                |                 | 8x             | 64bit/133MHz    |

| リンク性能                   | 1GByte/s×2        | 2GByte/s        | 1.25GByte/s×2  | 1.25GByte/s     |

| (実効データ転送速度)             | (4X)              |                 |                |                 |

| パケット転送方式                | VCT               | VCT             | VCT, SAF       | SAF             |

| トポロジ                    | Any               | Any             | Any            | Any             |

| ホストプロセッサ                | Xeon              | N/A             | Dual-Core Xeon | Opteron         |

|                         | 3.4GHz×2          |                 | 3.2GHz×2       | 2.2GHz with TOE |

| チップセット                  | N/A               | N/A             | Intel          | N/A             |

|                         |                   |                 | 5000P          |                 |

| ファームウェア                 |                   |                 | MX-10G 1.2.0h  |                 |

| 接続方式                    | InfiniScale       | N/A             | back-to-back   | back-to-back    |

|                         |                   |                 |                |                 |

| レイテンシ                   | 3.8µs             | $(1.29\mu s)$   | $(2.2\mu s)$   | 8.9μs           |

| スループット(片方向)             | 972MByte/s        | (954MByte/s)    | (1215MByte/s)  | 950MByte/s      |

| half of peak throughput | 1K - 2KByte       | (88Byte)        | (4K - 16KByte) | 256 - 512Byte   |

| スループット(双方向)             | 1932MByte/s       | (1884MByte/s)   | (2355MByte/s)  | N/A             |

VCT: Virtual Cut Through SAF: Store And Forward TOE: TCP Offload Engine

図 2.15 ALPU のブロック図

図 2.16 Cell Block のブロック図

本章では、DIMM スロット装着型ネットワークインタフェースである DIMMnet について述べる。まず、最初のプロトタイプである DIMMnet-1 について触れ、DIMMnet-1 を運用した結果、明らかになった問題点について述べる。そして、DIMMnet-2 の概要と、DIMMnet-1 の問題点の解決方法、及び試作基板について述べる。また、メモリスロットにネットワークインタフェースを装着することによって発生する問題点について、DIMMnet-2 の場合に解決可能であるかどうか考察する。最後に、本研究の目的について述べる。

### 3.1 DIMMnet-1

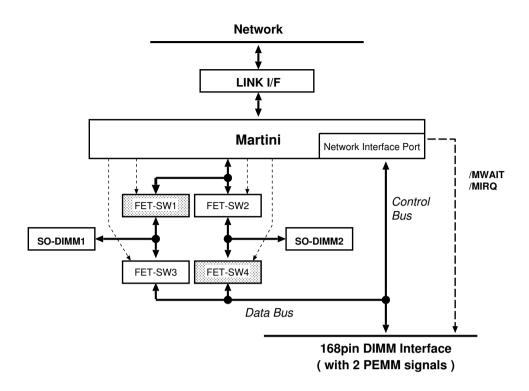

DIMMnet-1[35] は、MEMOnet の有効性を実証するために、DIMMnet のプロトタイプとして東京 農工大学中條研究室と新情報処理開発機構によって共同開発された、PC100 または PC133 仕様の DIMM スロットに装着するネットワークインタフェースである。 ネットワークインタフェースコ ントローラやネットワークスイッチには RHiNET-2 で用いられた Martini や RHiNET-2/SW を使用 していた。

DIMMnet-1 の主な仕様を表 3.1 に示す. また, その基本構造を図 3.1 に, 基板の概観を図 3.2 に示す.

ネットワークインタフェース上にはネットワークインタフェースコントローラである Martini と, 低遅延 FET (Field Effect Transistor) バススイッチを介してアクセス可能な 2 枚の SO-DIMM が搭載されている. ホストプロセッサからのデータは図 3.1 に示される Data Bus を通り, FET スイッチを介して SO-DIMM に転送される. 一方, Martini に対する要求は Control Bus を通り, Martini に直接転送される.

2枚の SO-DIMM はバンク構成になっている. Control Bus 経由で Martini にアクセスすることで FET スイッチを操作し、2枚の SO-DIMM を切り替えて (バンク切り替え) ホストプロセッサとネットワーク間で共有可能な 2 ポートメモリ構造を実現している. 図 3.1 は FET SW2 と FET SW3 が "ON" の状態であり、SO-DIMM1 がホストプロセッサ側、SO-DIMM2 がネットワーク側と接続され

表 3.1 DIMMnet-1 の主な仕様

| ホストとのインタフェース    | PC100,PC133 DIMM, 及び PEMM[94]           |

|-----------------|-----------------------------------------|

| コントローラ          | Martini                                 |

| 搭載メモリ           | PC133, SO-DIMM ×2                       |

| 搭載可能 SO-DIMM 容量 | 64MByte ~ 1GByte                        |

| 通信リンクスループット     | 各方向 8Gbps (全二重)                         |

| リンク性能           | 800MByte/s (PC100), 1024MByte/s (PC133) |

図 3.1 DIMMnet-1 の基本構造

ている様子を示したものである.

メモリバス側のインタフェースは、日本電子機械工業会規格の"プロセッサ搭載メモリ・モジュール (PEMM) 動作仕様標準 [94]"にも対応しており、PEMM で追加された2つの信号 (メモリへのアクセスを待たせる信号と割り込み信号) も有する.

#### 3.1.1 DIMMnet-1 の問題点

DIMMnet-1 の運用の結果、次のような問題点が明らかとなった.

- ネットワークインタフェースコントローラである Martini が基本的な RDMA read/write の機能しか提供していなかったため、複雑な処理はコントローラ内部のオンチッププロセッサを用いてファームウェアで実現する必要があった。しかしながら、オンチッププロセッサの性能が低かったため、複雑な処理を行うと通信性能が低下してしまっていた。

- DIMMnet-1 は PC133 の規格の SDR-SDRAM バスに対応可能なように設計されたが, 実際 には PC100 の場合にのみ安定して動作した. ネットワークインタフェース上の SO-DIMM に対するアクセスを FET スイッチを介して行う構造になっていたことが原因と考えられる. FET スイッチにより, 本来メモリスロットに想定されていない容量性負荷が加わってしまい, PC133 の規格では安定動作しなかったものと推測される. そのため, DIMMnet-1 の構造ではより高速な DDR-SDRAM バスなどには対応できないと言える.

DIMMnet-2 ではこれらの問題を解決するために、ネットワークインタフェースコントローラで 行う処理をすべてハードワイヤードで実現し、ネットワークインタフェース上の SO-DIMM に対し

図 3.2 DIMMnet-1

てはホストプロセッサから直接アクセスできない構造を採用する. 次節でこれらの詳細について述べる.

### 3.2 DIMMnet-2

DIMMnet-2 プロジェクトは DIMMnet-1 の経験を活かして次世代のネットワークインタフェースを開発し、より低コストで高性能な PC クラスタを実現することを目標として 2002 年度に立ち上げられた [95].

メモリバスに接続し、ネットワークインタフェース上にネットワークインタフェースコントローラのほかに SO-DIMM を搭載する点では同様であるが、DIMMnet-2 では様々な改良が施されている。 DIMMnet-1 と DIMMnet-2 の相違点を以下にまとめる.

### • DDR-SDRAM バスへ接続

DIMMnet-2 のプロジェクトが開始された 2002 年度には PC における主記憶の主流が DDR-SDARM に移り変わっていたことから, DIMMnet-2 は DDR-SDRAM バスに接続する. また, ネットワークインタフェース上に搭載されるメモリも DDR SO-DIMM となっている.

● ホストからネットワークインタフェース上の SO-DIMM への間接アクセス方式の採用 DIMMnet-1 における FET スイッチの問題から, DIMMnet-2 ではネットワークインタフェース上の SO-DIMM に対して直接アクセスせず, ネットワークインタフェースコントローラ内 部のバッファやレジスタを介してアクセスする間接アクセス方式を採用した. このようにすることで, SDR-SDRAM バスよりも高速な DDR-SDRAM バスに対応可能であり, さらには,

図 3.3 間接アクセス方式

より高速な DDR2-SDARM バスにも対応可能であると考えられる.

また、ローカルのネットワークインタフェース上の SO-DIMM とリモートの SO-DIMM の 双方に対するアクセスがコントローラ内部のバッファやレジスタを介して行われるようにな るため、双方に対して、統一した方式でアクセスすることが可能となる。

図 3.3 に間接アクセス方式の概略を示す. ネットワークインタフェース上の SO-DIMM に対して書き込みを行う際には.

- (a) コントローラ内部のバッファにデータを書き込む.

- (b) そのデータを SO-DIMM に転送する要求を要求発行レジスタ (Command Register) に発行する.

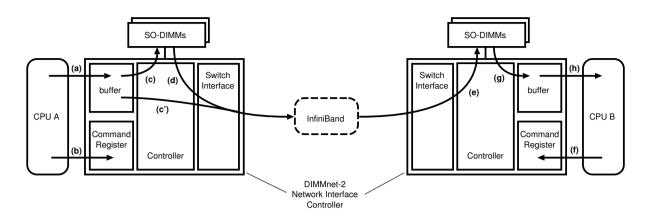

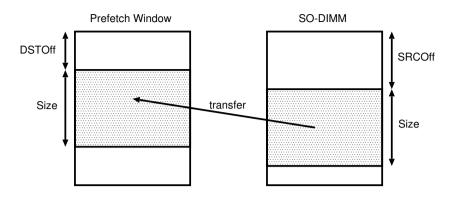

という手順を踏むことで実行される. リモートの SO-DIMM にデータを転送する際には, そのような要求を発行することでバッファからネットワークにデータが送出される (c'). バッファからではなく, ローカルの SO-DIMM からリモートの SO-DIMM にデータを転送することも可能である  $(d\rightarrow e)$ . 要求発行レジスタに SO-DIMM のデータを読み出す要求を発行すると (f), SO-DIMM からコントローラ内部のバッファにデータが転送される (g). このデータをホストから読み出すことで (h), SO-DIMM 内部のデータを参照することができる.

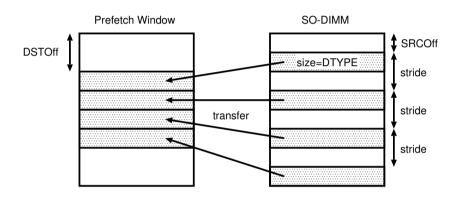

ネットワークインタフェース上の SO-DIMM への不連続アクセスのハードウェアサポート コントローラ内部のバッファとネットワークインタフェース上の SO-DIMM 間の転送機能 を拡張し、ベクトル型スーパーコンピュータで行われているような不連続領域に対するアク セスをハードウェアでサポートする [96][97][98].

このような機能を追加することによって、ホストプロセッサのキャッシュのヒット率やメモリバスの利用効率を向上させることが可能になり、DIMMnet-2をネットワークインタフェースとしてではなく、高機能なメモリモジュールとして用いることでアプリケーションの性能を向上させることが可能となる(図 3.4).

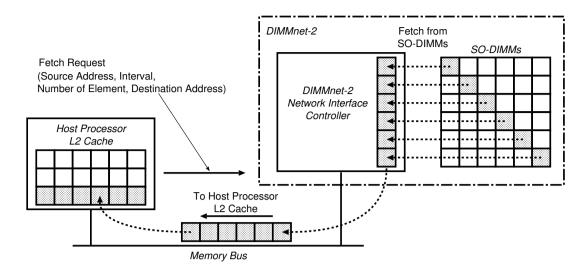

図 3.4 は、ホストプロセッサがネットワークインタフェース上の SO-DIMM 領域のうち、斜線部分のデータを必要としている場合のプリフェッチの動作を示したものである。本来、このように不連続な領域のデータを必要とする場合、ホストプロセッサは最大で、必要とするデータの個数回だけメモリアクセスを実行する必要がある。しかし、近年の PC におけるプロ

図 3.4 不連続アクセス機構

セッサでは L2 キャッシュのキャッシュラインサイズ単位でデータの読み出しを行うため、メモリバスを流れるデータや L2 キャッシュに格納されるデータのうち、ホストプロセッサが必要とするデータが含まれる割合が低下し、メモリバスの利用効率や L2 キャッシュのヒット率が低下する.

それに対して DIMMnet-2 は、ホストプロセッサからはデータ間の間隔 (インターバル) や要素数を指定したアクセス要求を 1 回発行するだけで、DIMMnet-2 のコントローラが必要なデータを SO-DIMM から読み出し、ホストプロセッサから直接アクセス可能な位置にある、コントローラ内部のバッファに格納する。ホストプロセッサはこのバッファからデータを読み出す。これにより、メモリバスの利用効率や L2 キャッシュのヒット率が改善される。

### • 商用コンポーネントの採用

ネットワークスイッチやケーブルといった、ネットワークインタフェース以外のコンポーネントには標準的な規格である InfiniBand の製品を採用し、独自規格の製品を用いていた DIMMnet-1 と比較して汎用性の向上とコストの低減を図っている.

#### 3.2.1 DIMMnet-2 試作基板

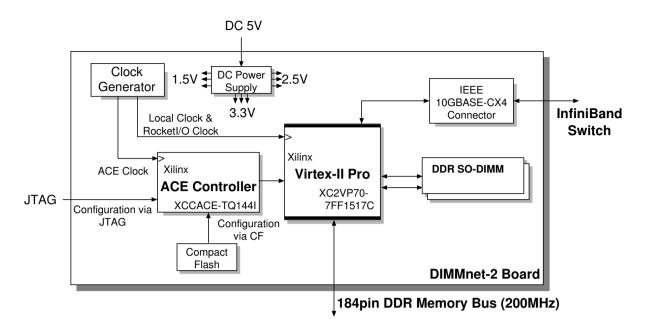

DIMMnet-2 はネットワークインタフェースコントローラに FPGA を搭載した試作基板を用いて研究・開発が行われている [11][12]. 内部論理の変更が可能な FPGA を用いることで,様々な機能の実装や検証を容易にしている. 図 3.5 に試作基板の構成図を,図 3.6 に概観を示す.

#### • Xilinx Virtex-II Pro XC2VP70-7FF1517C

ネットワークインタフェースのコアとなるコントローラ部は Xilinx 社 [99] の Virtex-II Pro XC2VP70-7FF1517C[93] 上に実装される. このチップは 8,272 個の Configuration Logic Block (CLB) と 5,904Kbit の内部 RAM (BRAM: Block RAM), 964 本のユーザ I/O ピンを持っており, さらに PowerPC を 2 個, RocketIO トランシーバ [100] を 16 個備えた, Virtex-II Pro の中

図 3.5 DIMMnet-2 試作基板の構成図

でも大規模でハイエンドな FPGA である.

RocketIO トランシーバは InfiniBand, Fibre Channel や Gigabit Ethernet に対応する高速シリアル I/O インタフェースであり、これを利用して InfiniBand (4X:10Gbps) に接続する.

### • Xilinx System ACE Controller

FPGA のコンフィギュレーションには Xilinx 社より提供されている, 大規模 FPGA のコンフィギュレーションソリューションである System ACE Compact Flash[101] を用いている. Virtex-II Pro のような大規模な FPGA には大容量のコンフィギュレーションメモリが必要となる. そのため, コンフィギュレーションメモリに PROM を用いると部品点数が増加し, 基板面積を圧迫してしまう. また JTAG 経由のコンフィギュレーションは複数のノードから構成される PC クラスタを構築した場合に使い勝手が悪いため, コンパクトフラッシュからのコンフィギュレーションを採用した.

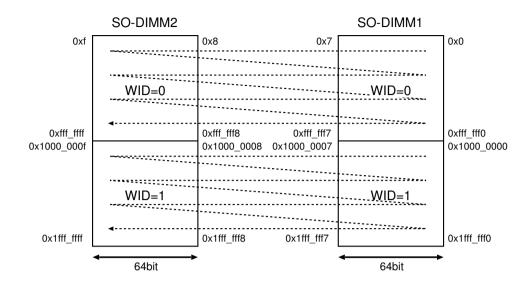

### • DDR SO-DIMM × 2

ネットワークインタフェース上にはノート PC 用の汎用メモリである 200pin DDR SO-DIMM が 2 枚搭載される. これらは通信用のバッファに使用されるほか, ホスト PC のデータ記憶 領域として用いられる. SO-DIMM を 2 枚搭載し, それぞれの SO-DIMM に対して FPGA から独立にアクセスすることで, Dual Channel 動作を実現でき, SO-DIMM アクセス時のスループットが向上する.

DIMMnet-2 は DDR-SDRAM メモリバスに接続されるため、最大で PC-3200 の規格に対応したメモリバスに装着される。この場合、ホストから DIMMnet-2 のコントローラ内部へのバッファに対しては PC-3200 の速度 (3.2GByte/s) でアクセスされることになる。もし、転送先である SO-DIMM が SDR SO-DIMM であった場合、PC133 の SO-DIMM を 2 枚使用して Dual Channel 動作させた際の最大転送スループットは 133 [MHz]  $\times$  64 [bit]  $\times$  2 (Dual Channel) = 2GByte/s となり、ホストからのデータ転送速度に比して、SO-DIMM への転送速度が低く、

図 3.6 DIMMnet-2 試作基板

SO-DIMM へのアクセスがボトルネックとなる. このことから, DDR SO-DIMM を採用した. 試作基板では 256MByte の SO-DIMM を 2 枚, 計 512MByte 分のメモリを搭載しているが, より容量の大きい SO-DIMM を搭載することで PC のメモリスロット 1 本当たりに搭載可能な最大容量のメモリよりも大規模なメモリ空間を提供することが可能である.

#### • IEEE 10GBASE-CX4 Connector

InfiniBand スイッチとの接続のために IEEE 10GBASE-CX4 のコネクタを搭載している. 従って, FPGA 内部の論理を変更することで, InfiniBand のみならず, 10GbE にも接続することが可能である.

#### • DDR Host Interface

PC の DDR-SDRAM スロットに装着可能とするために, 184pin DDR-SDRAM インタフェースを備える.

試作基板は PC のメモリバスに装着するため、PC 起動時に BIOS によりアクセスされる. その際に正常に PC を起動させるには、FPGA が実際のメモリのように振る舞い、BIOS のアクセスに応答しなければならない. 従って、試作基板を運用する場合は、電源を投入してから BIOS によるメモリバスへのアクセスが始まるまでにコンフィギュレーションが完了している必要がある. マザーボードによってはコンフィギュレーションが間に合わない場合があり、その場合はコンフィギュレーションが完了した後に PC をリセットする必要がある. PC リセット時にはメモリバスへの電源供給は絶たれないため、FPGA のコンフィギュレーションは保持されたままとなる.

試作基板は FPGA を用いているため、高い動作周波数での稼働が困難である。 そのため、ホスト側のインタフェースを 100MHz で動作させることで PC-1600 の規格でのみ、動作可能としている.

# 3.3 メモリスロットにネットワークインタフェースを装着することによる 問題点

メモリスロットにネットワークインタフェースを装着することで汎用 I/O バスに装着した場合よりも低レイテンシ, 高スループットな通信を実現できると考えられるが, メモリスロットを使用することによるデメリットも存在する.

### 3.3.1 PC に搭載可能な主記憶の最大容量の問題

一般的な PC に搭載されているメモリスロットは,2~4本程度であり,ネットワークインタフェースをメモリスロットに装着すると,その分だけ主記憶として使用できるメモリが減ってしまうことになる.

しかし、DIMMnet-2 はネットワークインタフェース上に大容量の SO-DIMM を搭載しており、DIMMnet-2 同士をネットワークで相互接続することで大規模なメモリ空間を提供することが可能である。そのため、科学技術計算などのスーパーコンピュータを必要とするアプリケーションにおいては、アプリケーションで使用するデータのすべて、または一部をネットワークインタフェース上に展開されるメモリ空間に配置し、演算に必要なデータをその都度ホスト側に読み出すことで、メモリ容量の欠点を補えると考えられる。

また、一般的な PC に搭載可能な最大メモリ容量は高々4~8GByte 程度であり、PC を用いて大規模なアプリケーションを動かすには、PC クラスタのように複数の PC を使用することで広いメモリ空間を実現する必要があるため、DIMMnet-2 によってメモリスロットを消費することに対するデメリットは大きな問題とならないと思われる。 さらに、疎行列を含む連立方程式など、メモリに対して不連続なアクセスを伴うアプリケーションにおいては不連続アクセスをサポートしているDIMMnet-2 を用いることで高い効果を期待できる [96][97][102][103][104].

### 3.3.2 Dual Channel 動作への対応の問題

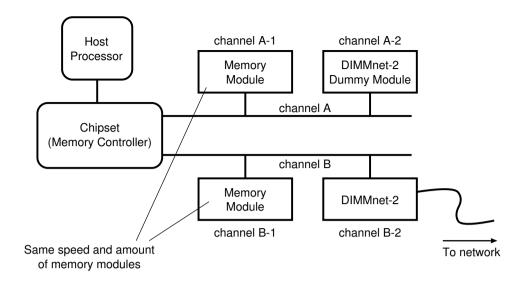

DDR-SDRAM が PC の主記憶に採用されるようになってきた頃から, 主記憶へのバスを 2 系統搭載し, Dual Channel 動作が可能なチップセットが PC に搭載されてきた. Dual Channel はそれぞれのメモリバス (チャネル) に同時にアクセスを行うことでメモリバスのスループットを 2 倍にする技術である. Dual Channel 動作には, それぞれのチャネルに同一の速度, 容量を持ったメモリモジュールを装着することが求められる.

しかし、DIMMnet-2 は通常のメモリモジュールとは異なるため、Dual Channel 動作でのメモリアクセスができなくなり、メモリバスのスループットが低下するという問題がある。 Dual Channel 動作を可能にするための対応として、

- DIMMnet-2 をそれぞれのチャネルに搭載する.

- DIMMnet-2 が装着されているチャネルと対になるメモリスロット $^{(\mbox{$\pm$}\mbox{$1$})}$ に DIMMnet と同じ SPD 情報を持つダミーモジュールを装着する (図 3.7).

ということが考えられる. しかしながら, DIMMnet-2 を 2 枚搭載し, Dual Channel 動作を実現した場合, 1 台のホストに LID が 2 つ割り振られてしまう, 2 枚の DIMMnet-2 へ同時にアクセスしてし

図 3.7 Dual Channel 動作への対応

まうなど、ホスト側からの扱いが複雑になるという欠点が存在する.

## 3.4 本研究の目的

本研究では DIMMnet-2 ネットワークインタフェースコントローラの設計, 及び実装を行い, 汎用 PC を用いた場合でも DIMMnet-2 と組み合わせることで, サーバやワークステーションと PC クラスタ向けインターコネクトを組み合わせたシステムに匹敵する通信性能を達成することを目的とする.

通信レイテンシに関してはメモリバスを利用することで、汎用 I/O バスを用いたインターコネクトよりも低くすることは容易であると考えられる。しかし、主記憶上に存在するデータを転送する際に高いスループットを得るのは難しいと推測される。主記憶と DIMMnet-2 が共にメモリバスに存在するため、主記憶のデータを DMA で DIMMnet-2 に転送することはできず、また逆に、DIMMnet-2 上のデータを主記憶に DMA で転送することもできない。そのため、主記憶と DIMMnet-2 との間のデータ転送は必然的に PIO になるため、一般に高いスループットは期待できない。本研究では PIO 通信でも高いスループットを達成可能とするために、複数の PIO 通信処理をオーバラップさせる手法を提案する。この手法の有効性は 6 章の評価を通して示す。

また、2.3 節で述べたメッセージ通信支援機構の問題点を解決した通信機構を 7 章で提案し、DIMMnet-2 ネットワークインタフェースコントローラへ実装する. そして、DIMMnet-2 を用いた評価から、通信性能がどの程度改善されるのかを示す.

# 第4章 DIMMnet-2ネットワークインタフェース コントローラの設計

本章では、DIMMnet-2 ネットワークインタフェースコントローラの設計について述べる. 本章で述べる内容は DIMMnet-2 試作基板を対象としており、ロジックはすべて FPGA に実装する.

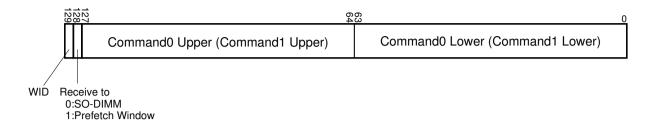

本章以降, アドレスやビットフィールドの表記で様々な形式の数値表現を用いる. ビット幅が重要となる値に関しては HDL (Hardware Description Language) 的な表現を用い, "[ビット幅]'[基数プリフィックス][数値]"の形式で表す. 基数プリフィックスは 16 進数の場合に h, 2 進数の場合に b となる. 例えば, 10 進数の 256 を 16 bit の 16 進数で表現すると, 16 h0100 となる. また, ビット幅が重要とならず, 数値のみに意味がある場合はスクリプト言語的な表現を用い, "[基数プリフィックス][数値]"の形式で表す. 基数プリフィックスは 16 進数の場合に 0x, 2 進数の場合に 0b となる. 例えば, 10 進数の 256 を 16 進数で表現すると, 0x100 となる. これらの数値は場合により, 4 桁ずつアンダースコア (\_) で区切る.

さらに、DIMMnet-2内部のレジスタをほかの語句と区別するために Sans Serif フォントを用いて表記する. 例えば、DIMMnet-2の内部にはネットワークの MTU 値を設定するための MTU という名称のレジスタが存在するが、MTU と表記されていればレジスタを指し、MTU と表記されていれば一般的な Maximum Transmission Unit のことを指す.

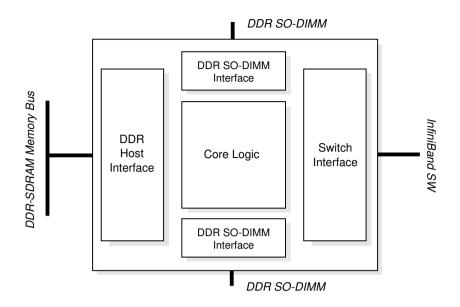

### 4.1 DIMMnet-2 ネットワークインタフェースコントローラの概要

DIMMnet-2 ネットワークインタフェースコントローラは汎用プロセッサを搭載せず、すべての処理をハードワイヤードで実現する. 一般にネットワークインターフェースコントローラはホストプロセッサに比べ、大幅に低い動作周波数で動作するため、汎用プロセッサ上のファームウェアで通信処理を実現するとレイテンシが大きくなると考えられるためである.

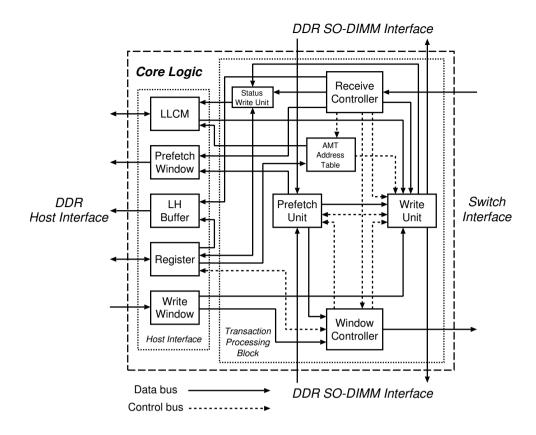

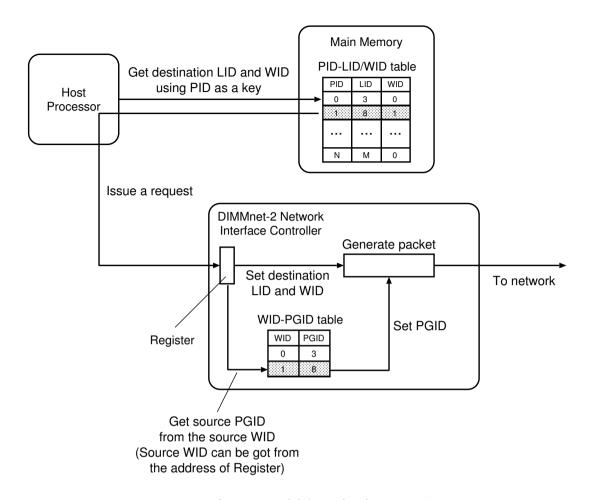

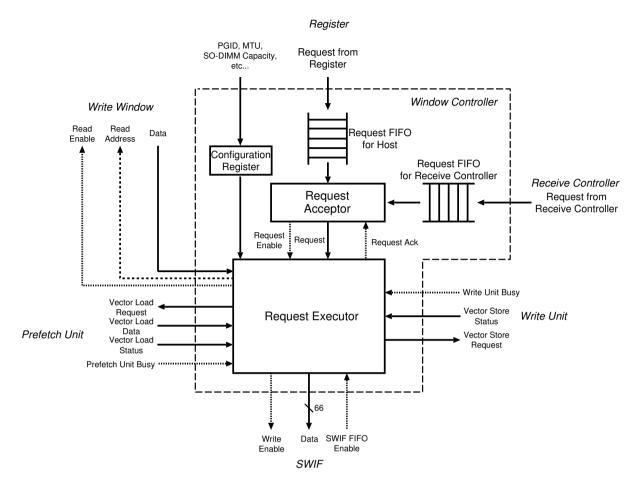

図 4.1 は, DIMMnet-2 ネットワークインタフェースコントローラ部のブロック図である. コントローラ部は大きく分けて, 4 つのブロックから構成される.

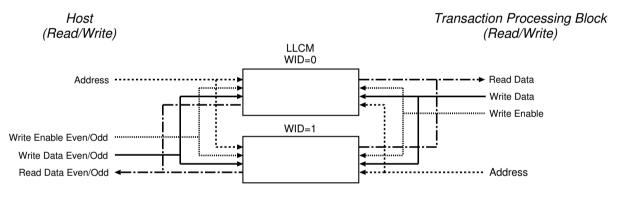

### • DDR Host Interface

ホストプロセッサとのトランザクションを処理するブロックである. ホスト側は DDR メモリのプロトコルに従って動作する. つまり, データの転送はクロックの立ち上がりと立ち下がりの両エッジに対してそれぞれ 64bit ずつ行われる. これに対し, コントローラ内部はクロックの立ち上がりのみの片エッジで動作する. そこで, DDR Host Interface は, この 64bit 幅両エッジのデータを 128bit 幅 片エッジデータへの変換を行う. また, 128bit 幅 片エッジデータから 64bit 幅 両エッジデータへの変換も行う.

#### • DDR SO-DIMM Interface

図 4.1 コントローラ部のブロック図

ネットワークインタフェース上の DDR SO-DIMM へのアクセスを制御するブロックである. Core Logic (後述) からの片エッジのデータ転送を DDR SO-DIMM への両エッジ転送に変換する. また, この逆の変換も行う.

#### • Switch Interface (SWIF)

InfiniBand ネットワークとのインタフェースである. Core Logic で生成した DIMMnet-2 独自形式のパケットを InfiniBand パケットでカプセル化し、ネットワークにパケットを送出する. また、ネットワークから受信した InfiniBand パケットを DIMMnet-2 独自形式のパケットにアンカプセル化する. End-to-End の再送機構を持ち、SWIF 内部の InfiniBand のレイヤで再送制御を行うことで、DIMMnet-2 のレイヤはネットワークのエラーに関与せずに済む構造になっている.

#### Core Logic

ネットワークインタフェースの制御部である. 送信パケットの生成や受信パケットの解析といった通信処理や, SO-DIMM Interface へのアクセス要求の制御を行う.

InfiniBand のネットワークを流れる信号は 1X 当たり 2.5Gbps であり, Virtex-II Pro に内蔵される RocketIO は入力された信号を 20 倍の周波数で出力する [100]. そのため, SWIF は 125MHz で動作させる必要がある. SWIF 以外のブロックはホスト側の周波数に合わせるために 100MHz で動作させる.

DDR Host Interface, 及び DDR SO-DIMM Interface は日立 JTE が開発を担当し, それを元に本研究で DIMMnet-2 向けに変更を加えた.

SWIF は東京農工大が開発を担当した。DIMMnet-2ではSWIFをCore Logic から分離し、DIMMnet-2独自形式のパケットをInfiniBand パケットでカプセル化して、ネットワークに送出する。このような形式ではカプセル化/アンカプセル化の分だけレイテンシの増大を招くため、本来ならばDIMMnet-2独自形式のパケットを用いずに、InfiniBand パケットを Core Logic で直接生成した方がレイテンシ

図 4.2 Core Logic 部のブロック図

の削減という点では有利である. しかしながら, SWIF のようにインターコネクトに依存した部分を分離することで, この部分の変更のみで別のインターコネクトへ対応することが可能となり, 汎用性, 柔軟性という点で優れる.

本研究では Core Logic の開発を担当した. PIO 通信を用いた高スループットな通信を実現するためには、ネットワークインタフェースコントローラ内の各モジュールを独立して動作可能にし、各処理をオーバラップ可能にする必要がある. また、ホストプロセッサからのアクセス時に高いスループットが得られるようにホストインタフェース部を設計する.

次節以降では Core Logic の設計について述べる. メッセージ通信支援機構の設計については 7章で述べる.

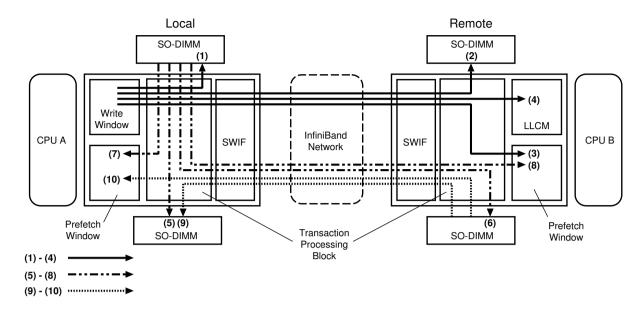

# 4.2 Core Logic の設計

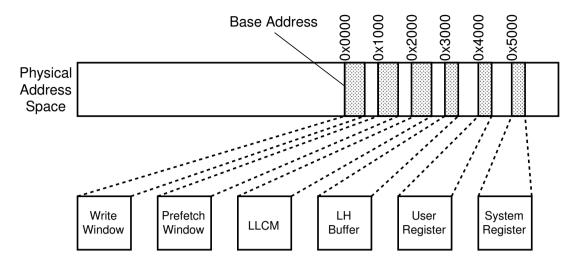

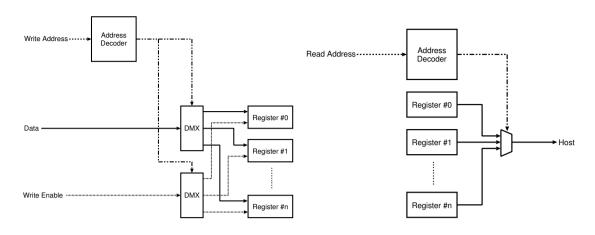

図 4.2 に Core Logic のブロック図を示す. Core Logic は大きく分けて, ホストから直接アクセス されるホストインタフェース部とパケットの送受信や SO-DIMM へのアクセスを行う要求処理部 から構成される.

|                 |                 |            | •          |

|-----------------|-----------------|------------|------------|

| Module          | Attribute       | Host       | Controller |