# 誘導結合を用いたチップ間無線通信 インタフェース

2007年11月

溝 口 大 介

#### 本論文の構成と内容

近年,携帯端末が普及し,より高性能な端末が求められている.端末の性能は内蔵されている半導体チップにより決まる.チップには,高性能化,メモリの大容量化,低電力化,低コスト化が求められる.従来,端末等のシステムを構築する際には,ボード上にプロセッサやメモリのチップを搭載して実現してきた.しかし,この実装方法では,システムの処理性能を,チップ間のデータ転送帯域が律速してしまう問題があった.また,チップ本体に比べパッケージの容積が大きいために,搭載チップ数が限られてしまうという問題があった.

現在、これらの問題を解決するために、システムオンチップ(SoC)やシステムインパッケージ(SiP)の研究・開発がなされている。SoC は、システム全体をチップ上に集積する技術で、バス帯域を上げやすく、性能を上げやすいという利点がある。しかし、メモリやアナログ回路を混載する場合、製造工程が複雑になり、コストが増大する。また、チップ面積が大きくなるため、歩留まりが低下し、コストが増大してしまう。SiP は複数のチップを1つのパッケージに納める技術で、異なるプロセスで製造されたチップを集積する事が可能である。これにより、プロセッサやメモリ、アナログ回路を SoC より安価に1 パッケージに収納する事ができる。また、各チップの面積が SoC より小さいため歩留まりが向上する。さらに、良品の選別後にパッケージに実装するため、SoC に比べ、システム全体の歩留まりが向上するという利点がある。この半面、パッケージ内のチップ間の接続はワイヤボンディングやマイクロバンプであり、SoC に比べバンド幅で劣ってしまう。そこで本研究では、SiP 内のバンド幅を向上するために、誘導結合を利用したチップ間無線通信インタフェースを提案し、その実用化を目指して基礎技術を確立する事を目的とする。

第 1 章は,序論であり,従来のチップ間通信技術の問題点と,これを解決するために行われている近年の研究動向についてまとめ,本研究の位置付けを明確にした.

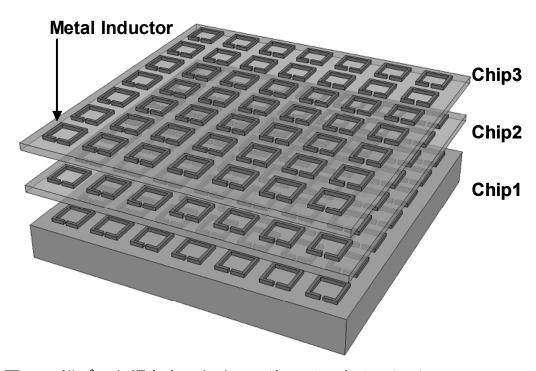

第2章では,誘導結合を用いたチップ間無線通信方式を提案し,その物理層, およびプロトコルの設計について,低電力化の検討を行った.提案した通信方 式は,通信のチャネルにメタル配線で形成したインダクタを利用する.積層実 装された各チップ上のインダクタを垂直方向に位置合わせし,このインダクタ 間の誘導結合を利用して通信を行う.

第3章では,従来報告されていなかった,積層実装したチップ間の誘導結合のモデルを検討し,その精度を実験で評価した.評価は,実際に作成したチップの実測値と提案手法による計算値の比較により行った.この結果,実測値とモデルによる計算値はよく合致し,今後の回路設計に用いる事ができる事を確

#### 認した.

第4章では,第2章で述べた無線通信方式を実装するために,送受信回路を提案した.送信器はH-Bridge 回路を採用し,受信器はラッチつきセンスアンプで実現した.さらに,送受信のビットエラーレートを左右するセンスアンプのノイズマージンの取り方を議論した.

第5章では,第4章で述べた回路を実チップに実装し,実際にチップを積層 実装した状態で行った送受信実験の結果を報告した.試作したチップは 0.35μmCMOS 技術で設計し 積層実装の上チップは300μmに研磨した.この結果, 通信距離300μmで1.25Gbpsの通信に成功した.

第 6 章では,電磁界に着目したスケーリングについて述べた.スケーリングの比例定数を $\alpha$ とすると,プロセスの進歩によりチップ内の各パラメータを $\alpha$ に比例して縮小し,通信距離も $\alpha$ に比例して縮小できたとすると,2次元配列の総バンド幅は $\alpha$ <sup>3</sup>,1 ビットあたりの消費電力は  $1/\alpha$ <sup>3</sup>に比例する事がわかった.

第7章では,本論文の各章をまとめ,今後の課題を述べた.

## 目次

| 第1章 | 序論                  | 1  |

|-----|---------------------|----|

| 1.1 | 背景                  | 2  |

| 1.2 | 関連研究                | 3  |

| 1.3 | 本研究の目的と構成           | 5  |

| 第2章 | 誘導結合を用いたチップ間通信方式の提案 | 13 |

| 2.1 | 誘導結合を用いたチップ間無線通信手法  | 14 |

| 2.2 | 基本原理                | 14 |

| 2.3 | 通信方式検討              | 15 |

| 2.4 | 容量結合方式との比較          | 16 |

| 2.5 | 研究課題                | 18 |

| 第3章 | 誘導結合モデル             | 30 |

| 3.1 | 緒言                  | 31 |

| 3.2 | オンチップインダクタ          | 31 |

| 3.3 | 誘導結合モデル             | 33 |

| 3.4 | チップ間誘導結合の測定         | 33 |

| 3.5 | まとめ                 | 36 |

| 第4章 | 送受信回路               | 56 |

| 4.1 | 緒言                  | 57 |

| 4.2 | 送受信回路               | 57 |

| 4.3 | 受信器の感度調整            | 58 |

| 4.4 | まとめ                 | 60 |

| 第5章 | 実験                  | 70 |

| 5.1 | 緒言                  | 71 |

| 5.2 | 評価方法                | 71 |

| 5.3 | 実験結果                | 72 |

| 5.4 | まとめ                 | 73 |

| 第6章 | 磁界一定のスケーリング則        | 81 |

| 6.1 | 緒言                  | 82 |

| 6.2 | 誘導結合の式の解析           | 82 |

| 6.3 | スケーリング則の前提条件        | 83 |

| 6.4 | 磁界一定のスケーリング則        | 84 |

| 6.5 | スケーリング則の給証          | 85 |

| 6.6 | 周波数特性のスケーリング則            | 86  |

|-----|--------------------------|-----|

| 6.7 | まとめ                      | 86  |

| 第7章 | 結論                       | 98  |

| 7.1 | はじめに                     | 99  |

| 7.2 | 誘導結合を用いたチップ間通信手法の提案 (2章) | 100 |

| 7.3 | 誘導結合モデル (3章)             | 100 |

| 7.4 | 送受信回路 (4章)               | 101 |

| 7.5 | 実験 (5章)                  | 101 |

| 7.6 | 磁界一定のスケーリング則 (6章)        | 102 |

| 7.7 | 総括                       | 103 |

| 7.8 | 今後の展望                    | 104 |

| 謝辞. |                          | 106 |

| 研究對 | <b> </b>                 | 107 |

第1章 序論

## 1.1 背景

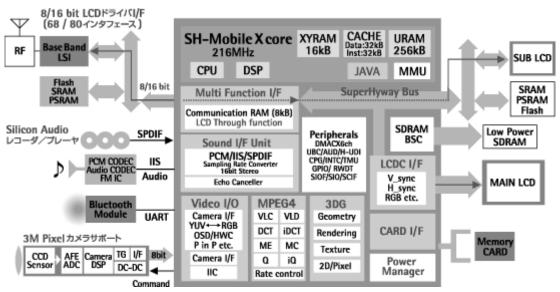

近年,多機能な携帯電話が普及している.現在の携帯電話は通話機能だけでなく,電子メールの送受信,Webブラウジング,デジタルカメラ,TV視聴・録画など,多数の機能を備えている.これらの機能を実現するためには,非常に多くの演算をリアルタイムに処理する必要がある.この処理をプロセッサ1個で実現すると,単位時間当たりの処理量を高める必要がある.これはプロセッサの周波数を高める事により達成できるが,周波数の2乗に比例して消費電力が増えるため,携帯端末等のバッテリ駆動の機器では現実的ではない.そこで,近年の携帯端末では,各処理に特化した専用回路を設け電力消費を抑えている.現在の携帯電話は,電力と処理速度のトレードオフから,全体の制御を行うプロセッサと,各機能の処理を行う専用回路,処理結果を格納するメモリを接続した構成をとっている(図 1.1).この様な構成は,携帯電話だけでなく,PDA やゲーム機,カーナビゲーションシステムなどの,小型の電子機器では一般的になりつつある.

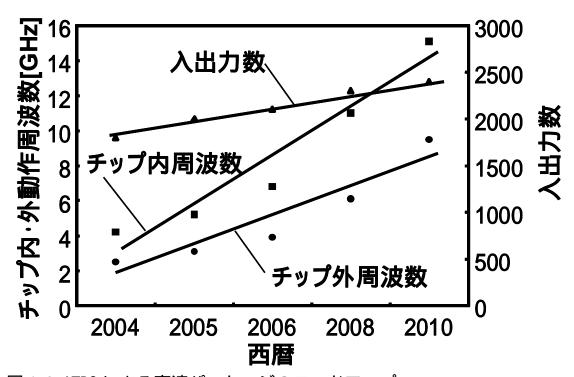

図1.1の様なシステムを構築する際には,従来,ボード上にプロセッサやメモリ,専用回路のチップを搭載して実現してきた.図1.2にITRSの予測する(Roadmap of leading-edge packages ITRS 2003 edition)チップ内の動作周波数とボード上の周波数,また,チップの入出力数をまとめた図を示す.図1.2中のチップ外の周波数がボード上のデータ転送に用いられるクロック周波数である.この周波数は最先端の高速シリアルリンク(2007年現在ではPCI-Express, XAUI等)を用いた場合の周波数を示している.最先端の高速シリアルリンクは消費電力が高く,組み込み用途には適さない.2007年現在の組み込み用途でのボード上のバス周波数は,数百MHzとなっている.また,ボードを用いると,面積の制約からバス幅(配線本数)を増やすことが難しい.このため,チップ間のバスバンド幅が限られ,システムの処理性能を,データ転送が律則してしまうという問題がある.また,パッケージの容積が大きいために搭載チップ数が限られ,メモリ容量を増やせないという制限がある.

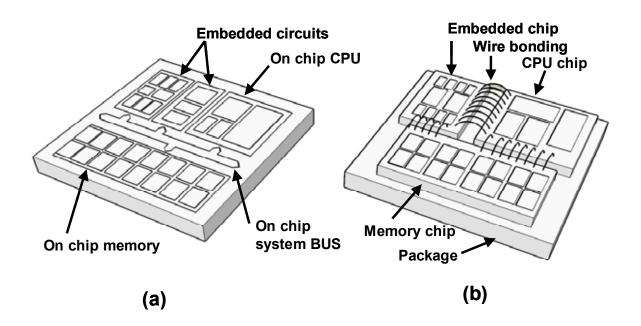

現在,これらの問題を解決するために,システムオンチップ(System On Chip, SoC)やシステムインパッケージ(System In Package, SiP)の研究・開発がなされている.SoC は,システム全体をチップ上に集積する技術で

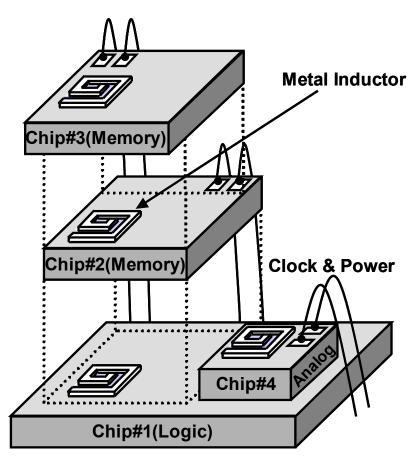

ある(図 1.3(a)).チップ内ではボード上に比べ,バスの転送速度を上げやすく,また,バス幅も大きく取る事が可能である.このため,SoC は性能を上げやすいという利点がある.しかし,メモリやアナログ回路を混載する場合,製造工程が複雑になり,コストが増大する.また,チップ面積が大きくなるため,歩留まりが低下し,コストが増大するという欠点がある.一方,SiP は複数のチップを1つのパッケージに納める技術で,異なるプロセスで製造されたチップを集積する事が可能である(図 1.3(b)).これにより,プロセッサやメモリ,アナログ回路を SoC より安価に 1 パッケージに収納する事ができる.また,各チップの面積が SoC より小さいため,歩留まりが向上する.さらに,良品の選別後にパッケージに実装するため,SoC に比べ,システム全体の歩留まりが向上するという利点がある.この半面,パッケージ内のチップ間の接続はワイヤボンディングやマイクロバンプであり,バスの転送速度とバス幅を大きく取ることが出来ず,SoC に比べバンド幅で劣ってしまう.

高性能,多機能,低電力で,低価格なシステムを構成するためには,SoCに比べ,SiPが向いていると考えられるが,唯一,バスバンド幅が不利である.SiP内のバンド幅向上が,システムの高性能化,高機能化,低電力化につながり,システムの付加価値を向上させる.このため,本研究では,SiP内のバンド幅向上を目標とし,新しいチップ間データ通信手法を提案する.

## 1.2 関連研究

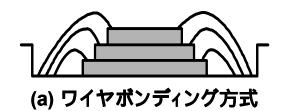

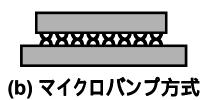

積層 SiP 内の接続については複数の研究が報告されている([1-5]). ワイヤボンディング方式 (図 1.4(a)) は,従来技術を応用しており,安価に接続できるため,すでにフラッシュメモリ等の製品に採用されている.ただし,この方法は,入出力がチップ端のみに限られ,また,長い配線を用いる事から寄生誘導成分が付き,帯域が制限されてしまう.この問題を解決するために,チップ間を物理的に2次元配列状の端子で接続する研究も報告されている([1-2]).[1]は,直径30μmの球状半田を60μmピッチで配列状に並べている(図 1.4(b)).この方式は,端子数を大幅に増やす事ができ,総バンド幅160Gbpsを達成している.ただし,この方式は,チップの回路実装面を向い合せた実装方法のみに適用でき,3層以上の積層チップには適用できない.[2]の貫通電極は(図 1.4(c)),30μmピッチでチ

ップ自体を貫通する導体を作成し,上下チップの電極を接続する.この方式では3層以上の積層チップに対応できる.ただし,穴の形成に時間がかかり,また,微細な物理的加工であるため歩留りも悪く,結果としてコストの増大を招く.また,物理的接触を用いて外部との入出力を行うと,寄生成分の影響で周波数を上げるのが困難となる.また,図1.2のロードマップより,チップ内周波数はチップ外周波数を引き離して行くため,物理的接触を用いてパッケージ外でチップ間を接続しても,チップ内外の速度の乖離のため,データ転送が処理性能を制限して行くと考えられる.さらに,チップの入出力ピン数の増加も,内部の周波数の増加と比較すると少ない.このため,ピン数を増やして周波数の差を埋める事も困難である.

これらの物理的な接続に対し、入出力数をチップの任意の場所に設ける 事が出来,物理的接続による寄生成分の影響を受けない,無線方式のチッ プ間接続が提案されている([3-5]).[3]は,本研究が目標としているデー タ伝送では無くクロック伝送であるが,チップ間をダイポールアンテナを 用いて,無線で伝送している.無線であるため,配線遅延が無く,少ない 位相ずれでクロックの分配に成功している.[4-5]は,チップの回路実装 面を向い合せ ,チップ上の電極間に生成される容量結合を利用し ,データ 通信を行っている(図 1.5). 論文[4]では, 2.4Gbps, 26mWで, 通信に成功 している.また,論文[5]では,1.27Gbps,3mWという,高速・低電力通 信を実現している.非接触通信は,物理的接触を用いる通信に比べ,原理 的に高速化・低電力化を行い易いという利点がある.機械的接触のある接 続方法では, 10 パッドと ESD 保護回路が必要となり, これらの回路に付 く寄生容量が高速化・低電力化の妨げになるからである.一方で,非接触 通信は,電磁波もしくは電界・磁界を用いた通信となるが,これらは距離 の2乗に比例して減衰する.通信距離が大きい場合,電磁波の減衰分を補 うために余分な電力を必要とし, IO パッドと ESD 保護回路の削減から得 られた低電力化の恩恵を相殺してしまう可能性がある.このため,論文 [4-5]では,対面実装を採用し,通信距離を最小限に抑えて,低電力化を 達成している.一方で,容量結合を用いた方式は,チップ本体を貫通した 通信は電力効率が低い可能性が高い.これは,距離に比例して容量が低下 するためであり、容量の減少に伴い、電力効率も低くなる、容量結合を用 いた報告では,対面通信以外の報告はなされていない.

以上の関連研究より,3層以上の積層チップ間で,物理的接触のない(歩留まり高,安価),2次元配列可能な通信手法が必要であると考えられる.

## 1.3 本研究の目的と構成

本論文では,上に述べた背景を踏まえ,SiP内のバスバンド幅向上のための新しい技術について述べる.目標として,通信速度は1.2Gbps以上,面積は100μm 以下を目指す.通信速度の目標は容量結合方式([5])以上を,面積の目標としては一般に用いられているPADの大きさ以下を目標の根拠とした.

下記に本論文の各章の概要を述べる.

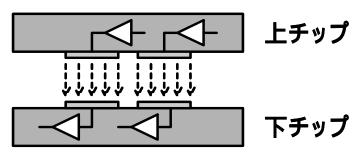

#### 第2章 チップ間無線通信方式の提案

本章では、提案手法であるチップ間無線通信手法の概要について述べる.本論文が対象とするのは、チップを縦に積層実装した SiP である.積層実装された上下チップ間の通信は、従来、ワイヤボンディングやマイクロバンプを用いて行ってきた.本章では、この通信手法に変わり、誘導結合を利用した通信手法を提案する.通信には、各チップ上に形成したインダクタを利用する.通信を行いたいインダクタの上下の位置を合わせておき、そのインダクタ間に生じる誘導結合を通信に利用する.本章では、さらに、通信の信号方式も提案する.また、容量結合方式との比較も行う.

#### 第3章 誘導結合モデル

提案するチップ間通信手法を実現するためには,まず,通信路である誘導結合の性質を理解する必要がある.しかし,従来,積層実装された上下チップ間の様な近距離の誘導結合について研究された例はない.このため,本章では,チップ間通信のための誘導結合のモデルを提案する.さらに,このモデルの正当性を,実チップを実際に積層実装を行い,誘導結合を直接ネットワークアナライザを用いて測定する事により,検証する.

#### 第4章 送受信回路

本章では、第2章で述べた無線通信方式を実装するために、送受信

回路を提案する.送信器はH-Bridge 回路を採用し,受信器はラッチつきセンスアンプで実現する.3 章で述べたインダクタのモデルを用いて,提案回路の SPICE シミュレーションを行い,通信が可能である事を検証する.さらに,製造ばらつきやクロックジッタを考慮に入れたタイミングマージンの評価を行い,所望のマージンを達成する回路パラメータの決定方法を議論する.

#### 第5章 実験

本章では,第4章で述べた回路を実チップに実装し,実際にチップを積層実装した状態で行った送受信実験の結果を報告する.試作したチップは3層金属配線0.35μmCMOS技術で設計し積層実装の上チップは300μmに研磨した.近年の高密度積層実装されたメモリチップは60mm程度の厚さであり,300μmという通信距離はチップ5層を通した通信に相当する.この結果,通信距離300μmで1.25Gbpsの通信に成功した.また,タイミングマージンの測定も行い,見積もりとほぼ同じマージンを測定できた.

#### 第6章 磁界一定のスケーリング

第6章では、電磁界に着目したスケーリングについて議論する.受信電圧一定という制約条件で、通信チャネル密度を上げて行く場合を想定する.受信電圧を計算する式を、インダクタの各パラメータから算出できる様式変形を行い、これらのパラメータがスケーリングファクターに比例して縮小しても、一定とできる事を示す.これにより、今後、プロセスが進歩した場合にも、提案する通信手法が有効であることを示す.

図 1.1 システム構成の一例 (ルネサステクノロジ社製携帯電話向けチップ SH-Mobile 3 と周辺回路).

図 1.2 ITRS による高速パッケージのロードマップ.

図 1.3 (a)SoC, (b)SiPの概念図.

(c) 貫通電極方式

図 1.4 SiP 内の,物理的接続を用いたチップ間接続.

図 1.5 容量結合を用いた SiP 間通信方式.

## 参考文献

- [1] T. Ezaki, K. Kondo, H. Ozaki, N. Sasaki, H. Yonemura, M. Kitano, S. Tanaka and T. Hirayama, "A 160Gbp/s Interface Design Configuration for Multichip LSI," *ISSCC Digest of Technical Papers*, pp.140-141, Feb. 2004.

- [2] J. Burns, L. McIIrath, Hopwood, C. Keast, D. P. Vu, K. Wamer, P. Wyatt, "An SOI-Based Three-Dimensional Integrated Circuit Technology," 2000 IEEE International SOI Conference, pp. 20-21, Oct. 2000.

- [3] K.Kim, H.Yoon, O.K.K, "On-chip wireless interconnection with integrated antennas," 2000 IEEE International Electron Devices Meeting, Technical Digest, pp485-488, Nov. 2000.

- [4] S. Mick, J. Wilson, P Franzon, "4Gbps High-Density AC Coupled Interconnection," *IEEE Proceedings of CICC*, pp. 133-140, Oct. 2002.

- [5] K. Kanda, D. D. Antono, K. Ishida, H. Kawaguchi, T. Kuroda, and T. Sakurai, "1.27Gb/s/pin 3mW/pin Wireless Superconnect (WSC) Interface Scheme," 2003 ISSCC Digest of Technical Papers, pp. 186-187, Feb. 2004.

# 第2章 誘導結合を用いたチップ間通信 方式の提案

## 2.1 誘導結合を用いたチップ間無線通信手法

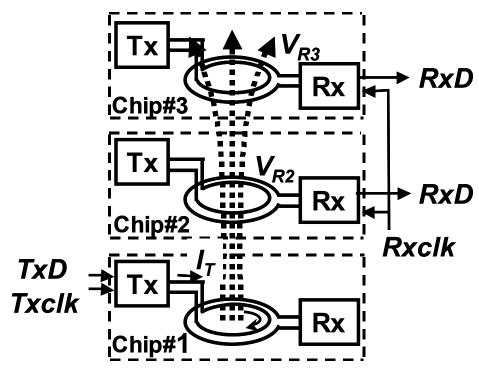

SiP内のチップ間の通信を高速で行うために,本研究では図2.1に示す様な通信形態を提案する.SiP内のチップが縦に積層実装され,それぞれのチップ上に通信用のインダクタを縦方向に位置合わせして実装しておく.このインダクタ間に形成される誘導結合を利用して通信を行う.この方式を用いると,データだけでなく,クロック,電源も供給することが可能である.本研究では,1章で述べた通りSiP内のバンド幅の向上を主たる目的とするため,データ転送について述べる.データレートは,1.2Gbps/ch以上を目標とする.

磁界の変化は半導体チップを貫通するため,3層以上の積層実装に対応できる.また,物理的接続を用いないため,接続に関する歩留まりの問題が生じない.また,物理的接続による寄生成分がないため,高速通信が期待できる.これらの利点について,1章で述べた他方式の接続手法と比較を行い,まとめた物を表2.1に示す.表中,容量結合方式の積層数は,論文報告のあった2層を採用している.2層以上の可能性もあるが,これは2.4章で議論する.帯域については,配線距離の長いワイヤボンディングの評価を「低」,距離が近いが寄生成分の影響のあるマイクロバンプ・貫通電極を「中」とした.歩留まりは,ワイヤボンディングは用いられている期間が長く,技術的レベルが高くなっているため「高」と評価した.表2.1の比較より,積層数・帯域・歩留まりの3つの観点から優れているのは,誘導結合方式だと結論付けられる.

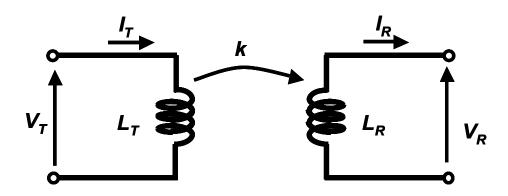

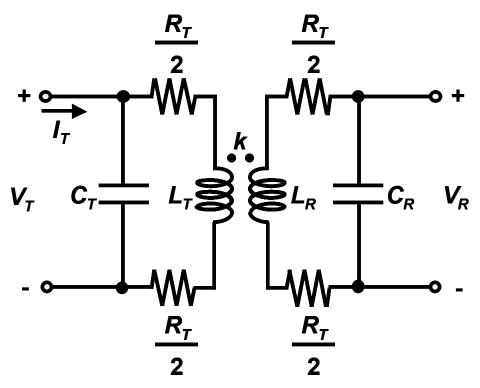

## 2.2 基本原理

通信に用いる誘導結合は,図 2.1 の様にトランスで表され,式(2.1)で示される電磁誘導の式に従う.両インダクタの結合の度合いを,結合定数kで表す.受信インダクタの両端には,送信電流 $I_r$ の時間微分値に,相互インダクタンスMを乗じた値が,受信電圧 $I_R$ として誘導される.

$$V_{R} = L_{R} \frac{dI_{R}}{dt} + M \frac{dI_{T}}{dt}, \qquad (2.1)$$

$$V_{T} = L_{T} \frac{dI_{T}}{dt} - M \frac{dI_{R}}{dt}.$$

(2.2)

結合定数 $k \geq M$ ,  $L_s$ ,  $L_r$ の間には,下式の関係が成り立つ.

$$k = \frac{M}{\sqrt{L_T L_R}}. (2.3)$$

本研究では,受信インダクタにはほとんど電流が流れないため,/ $_{R}$ =0と近似すると,式(2.1),(2.2)は次の様に表される.

$$V_R = M \frac{dI_T}{dt}, \tag{2.4}$$

$$V_T = L_T \frac{dI_T}{dt}. (2.5)$$

また,式(2.4)へ式(2.3)を代入し下記の様に表される.

$$V_R = k\sqrt{L_T L_R} \frac{dI_T}{dt}.$$

(2.6)

## 2.3 通信方式検討

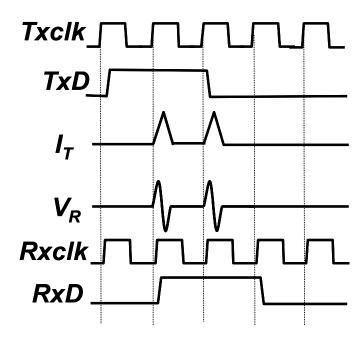

受信電圧が送信電流の時間微分で表される事を述べたが,本研究が前提としているのは,デジタルデータの送受信である.デジタルの 0/1 を表す High/Lowの電圧波形を,誘導結合を用いた通信に適した形に変換して送受信する回路が必要となる.この概念図を図 2.3 に示す.送信回路は,入力されたデジタルデータをインダクタの送信電流/元に変換し,受信器は受信電圧 V<sub>R</sub>をデジタルデータに復号する必要がある.変換の方法は複数考えられる.以下に,その方式を挙げる.

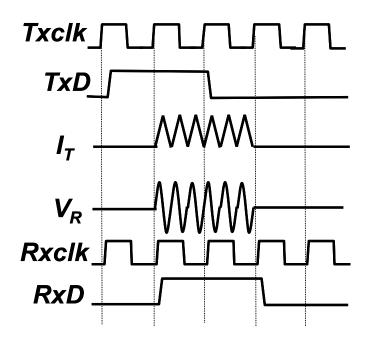

### (1) 振幅変調方式

High のデータがあるときのみ(もしくは Low のデータがある時のみ),送信電流を流す(図 2.4).本方式は電流を流さない極性のデータが続いた時には消費電力が小さくなる利点があるが,ノイズをデータと取り違う可能性がある.データの High/Low が同じ頻度で

出現すると仮定すると,送信電流を流す確率も1/2となる.

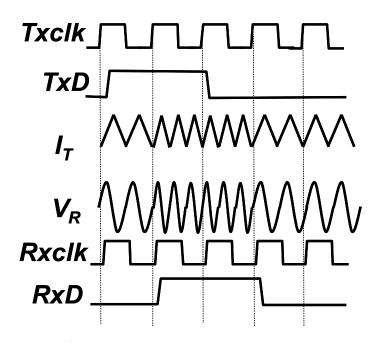

#### (2) 周波数変調方式

送信データに対応した周波数の送信電流を流す方式である(図 2.5).本方式は,ノイズに強い反面,常に電流を流しているため,電力的に不利である.

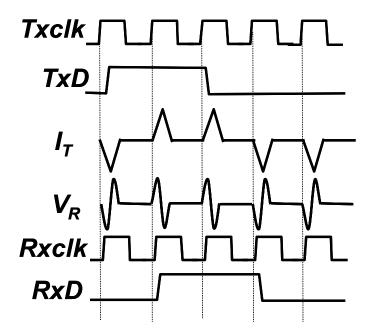

#### (3) パルス変調方式

(3-1) Bi-Phase 方式.データに応じた位相の送信電流を流す方式 (図 2.6).本方式は,毎クロック送信電流を流すため,電力的には不利である.反面,ノイズに強いという利点がある.

(3-2) Mono-Phase 方式 .符号に応じて送信電流を流す方式(図 2.7).本方式は, Bi-Phase に比べ,送信電流を流す頻度が下がる反面,電流を流さない符号が続くと,振幅変調方式と同様にノイズに弱い.

(3-3) Non-Return-Zero(NRZ)方式.データの遷移があるときのみ,データに応じた電流を流す(図 2.8)方式.本方式では,同じデータが続くと,まったく電力を消費しないという利点がある.ただし,前述のどの方式よりもノイズに弱い.

以上の5通りの方式はそれぞれトレードオフがあるが,本方式は結合定数が0.1前後になる予想であり,電力効率の面で不利である可能性が高い. このため,本研究では,送信電力削減を目的とし,(3-3)NRZ 方式を採用する事とした.

## 2.4 容量結合方式との比較

チップ間を無線で通信する手法は,1章で述べた容量結合方式がすでに存在する.新たな方式を主張するためには,従来方式より原理的に優れている必要がある.本節では,容量結合方式に対する,誘導結合方式の優位性について議論する.

最初に挙げられる利点として,プロセス技術のスケーリングの恩恵を得られる点にある,自己インダクタンスは巻き数に比例して増加する,式

2.6 より、受信電圧は、送信・受信インダクタの巻き数に比例することが わかる、このため、プロセス技術の進歩により配線層が増えると、受信電 圧の向上, つまり伝送効率が上がり, 消費電力を下げることができる. 容 量性結合方式では,最上位の配線層のみ利用するため,この効果は期待で きない.また,誘導性結合方式は電流モードの結合であるため,電源電圧 のスケーリングの影響を受けないという利点もある.誘導性結合は電圧モ ード結合であるため,電源電圧が下がると,伝送効率が下がってしまう. 以上の利点に加え、誘導性結合は伝送効率の面で容量性よりも原理的に 有利であり,3 層以上のスタックに適用したときに差が顕著となると考え られる、これは、電界の物理的特性に依存する、電界は、完全導体があっ た場合,静電遮蔽され,完全導体を貫通できない.半導体基板は完全導体 ではなく10 / 程度の抵抗値を持った導体であり、また、通信に用いる 電界の変化の周波数が高いため,電界は基板を貫通可能であると考えられ る.しかし,導体内で電界の電波を打ち消す力が働き,減衰が大きいと考 えられる.さらに,通信に利用する界の変化方向と,半導体素子内の材料 の特性から、電界を用いた通信は不利であると考えられる、スタックチッ プの層を重ねる方向を Z 方向とすると,容量性結合は電界の変化を Z 方向 に伝える.このとき,電界の変化はスタックチップの基板,酸化膜,配線 層を貫通するが,これらの材質の誘電率はそれぞれ大きく異なり,電界の 変化は不連続な境界を貫通することとなる.すると,境界面では反射が生 じ, 伝送効率が低下してしまう. 誘導性結合では磁界の Z 方向への変化を 利用するが,半導体チップ内の材質の透磁率はほぼ1であるため,反射が 生じにくい.以上の理由により,誘導性結合が伝送効率の面で優れている 可能性が高い.

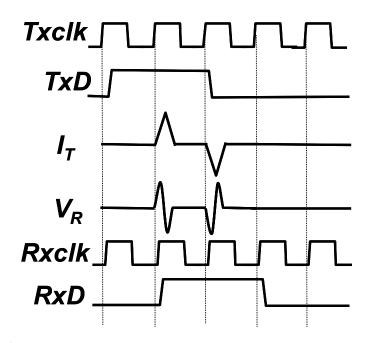

3 層以上の通信では、誘導結合を用いた通信が有利であることを原理的に検証するために、電磁界シミュレーションを行った.用いたシミュレータは、みずほ情報総研株式会社製 EMERGE である.EMERGE はマクスウェル方程式を、直接空間・時間領域での差分方程式に展開し逐次計算を行う有限差分時間領域(Finite Difference Time Division, FDTD)法を採用している.FDTD は、マクスウェル方程式を直接計算するため、計算量が膨大である一方、高い計算精度を持つ.FDTD 法では、一般的に、メッシュサイズを波長の20分の1以下にとると、誤差を0.3%以下に抑えられる事が知られている.シミュレーションで用いる周波数は1GHz前後(波長30cm)であり、解析領域のメッシュは1μm幅であるため、十分精度を保って解析することが可能である.図2.9 に、誘導・容量結合方式の比較の図を示す.この図は3層スタックチップをシミュレーションした結果の断面図を示

しており、(a)が誘導性結合の Z 方向の磁界分布、(b)が容量性結合の Z 方向の電界分布を示している.入力として 1 V ピークのガウシアンパルスを一番下のインダクタ(平板電極)に印加し、3 層目のスタックチップ上のインダクタ(平板電極)に生じる電位が最大となる瞬間の状態を比較した.容量結合の結果では、スタックチップの境界が見て取れるほど電界の変化(=減衰)が生じている.また、180μm離れた 3 層目の電極に生じる電圧は、0.4mV と非常に小さい値となっている.一方、誘導結合の磁界分布は、まったく境界面に影響を受けておらず、受信電圧も 65mV と、十分大きな値となっている.

以上より,誘導結合方式は,容量結合方式より原理的に有利である事がわかった.特に,回路実装面を上にして実装する場合や,3チップ以上の積層実装時に,有利である事がわかった.

## 2.5 研究課題

チップ間を誘導結合を用いて通信する研究は例を見ない.このため,従来報告されていない,下記技術が必要となると考えられる.

#### 1. チップ間の誘導結合検討

オンチップトランスフォーマ等の誘導結合モデルは存在するが,積層チップ間は例をみない.誘導結合のモデルの検討や,半導体基板の影響を検討する必要がある.

#### 2. 誘導結を用いた送受信回路

通信を実現するため,低電力,小面積な送受信回路を作成する必要がある.

### 3. 通信距離削減のためのチップ研磨技術

誘導結合は通信距離の2乗に比例して結合強度が減衰する.このため,通信に必要な電力を削減するためには,通信距離を削減する必要がある.

3については回路技術で対応できないため,他研究の成果を利用する.本研究では1と2について研究を行う.

図 2.1 インダクタを用いた積層チップ間無線通信概念図.

表 2.1 SiP 内接続方法の比較.

| 接続方式  |           | 積層数 | 帯域 | 歩留まり |

|-------|-----------|-----|----|------|

| 物理的接続 | ワイヤボンディング | 2以上 | 低  | 高    |

|       | マイクロバンプ   | 2   | 中  | 低    |

|       | 貫通電極      | 2以上 | 中  | 低    |

| 無線    | 容量結合      | 2   | 高  | 高    |

|       | 誘導結合      | 2以上 | 高  | 高    |

$L_T\!(L_{\!R}\!)$ :送信(受信)インダクタの自己インダクタンス $I_T\!(I_{\!R}\!)$ :送信(受信)インダクタに流れる電流 ${f k}$ :結合定数

図 2.2 誘導結合の等価回路.

図 2.3 スタックチップ間通信の概念図.

図 2.4 振幅変調方式.

図 2.5 周波数変調方式.

図 2.6 Bi-Phase 方式.

図 2.7 Mono-Phase 方式.

図 2.8 NRZ 方式.

図 2.9 電磁界シミュレーションによる誘導結合・容量結合の比較.

## 第3章 誘導結合モデル

## 3.1 緒言

誘導結合方式チップ間無線通信を実現するための基礎として,通信路である誘導結合の特性を知る必要がある.結合の特性を等価回路モデルとして表し,プロトコルや送受信回路の検討に用いるためである.誘導結合の等価回路モデルは,過去に十分な数の報告がなされているが,提案する通信手法を想定したモデルの報告は例を見ない.インダクタの実装形態が提案手法に近いアプリケーションとして,RFID やオンチップトランスフォーマが挙げられる.

RFID は誘導結合を利用してデータや電力の送受信を行う.使用周波数は 2MHz~3GHz と,提案手法に近い周波数帯を用いている.しかし,通信距離が数センチメートル~数メートルと,インダクタ間の距離が非常に大きい点が,提案する通信手法と異なる.提案する通信手法の通信距離は,数ミクロン~数百ミクロンである.通信距離の違いは,チャネル間の電磁界分布の違いを生み,提案通信手法のモデルには適用できない可能性がある.また,RFID は送信側と受信側でグランドの電位が共通でなくとも良いという違いがある.

オンチップトランスフォーマは,通信距離が0に近く,こちらも電磁界の状況やインダクタ間の容量結合の状況が違う.提案手法に比べると,誘導結合・容量結合の結合強度が強く,また,グランドが共通であるという違いがある.

提案する通信手法のプロトコルや送受信回路検討のために,提案手法にあった結合モデルが必要である.本節では,従来より提案されているインダクタモデルを元に,シンプルな誘導結合モデルを提案する.さらに,従来行われた事の無い,スタックチップ間の誘導結合をネットワークアナライザで測定し,提案モデルの正当性を検証する.

## 3.2 オンチップインダクタ

チップ上にメタル配線を利用して作成されたインダクタをオンチップ スパイラルインダクタと呼ぶ.このインダクタは,直径,巻き数,線幅, 配線間隔,配線総数を決めて設計する.これらのパラメータは,プロセスルールに従わなければならない.また,層間膜厚や基板抵抗等の様に製造プロセスに依存して一意に決まるパラメータもある.これらのパラメータにより,インダクタの自己インダクタンス,周波数特性が決定する.

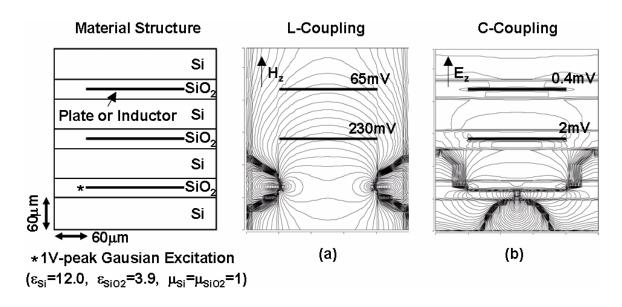

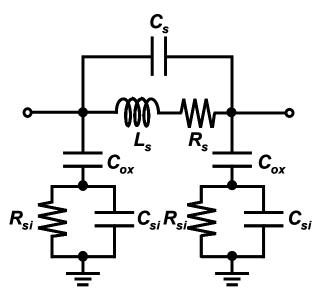

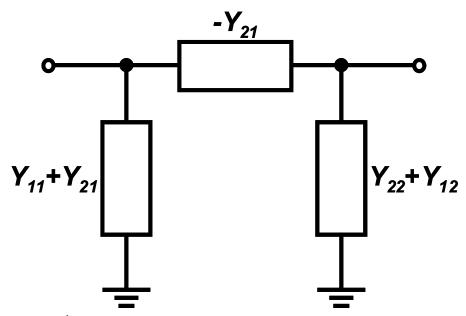

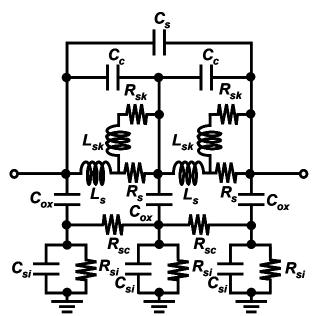

物理的なパラメータにより決まる特性を回路設計に用いるために ,等価 回路としてモデル化する研究が従来より行われている([1]-[3]).特に近 年では,無線通信回路にインダクタが数多く用いられ,高周波特性の厳密 なモデル化が求められている .現在までに考案されているインダクタのモ デルを図 3.1~3.3 に例示する.図 3.1 は,最低限の物理パラメータを反 映した最もシンプルな等価回路である.このモデルは,配線の表皮効果や 近接効果,基板の渦電流の効果等が考慮に入っていない.図3.1の各パラ メータをまとめると,図3.2の様になるため,このモデルは 型モデルと 呼ばれる. 型モデルに配線の表皮効果,近接効果,分布定数効果を入れ たモデルが図 3.2 である .このモデルは two- 型モデル([4])と呼ばれる . 図 3.3 の等価回路は高周波回路(RF)のために考案されたものであり,数十 GHz まで対応している. 本研究では 1Gbps 前後の通信を前提としており, two- 型ほどの精度は必要ないと考えられる.また,図3.1は3Gbps程度 まで精度を保てるという報告がなされている([4]).本研究では,用いる 通信の中心周波数が 1GHz であるため,図 3.1 よりももっとシンプルでよ い可能性がある.

図 3.1 のモデルは , (1) インダクタ部分の直列接続成分(( $L_s+R_s$ )// $C_s$ ) , (2)配線と基板間の容量( $\mathcal{C}_{ox}$ ), (3)基板のインピーダンス( $\mathcal{C}_{si}$ // $\mathcal{R}_{si}$ )から成 る.ここで,(1)のインダクタの直流成分で消費されるパワー $P_s$ のオーダ を考察する.本研究で用いるインダクタの平均的なパラメータとして,数 回巻きの 100μm径のインダクタを用いたと仮定する.この場合Lsは数nH,  $R_s$ は数十 ,  $C_s$ は数百fFとなる.オーダの考察のために,  $L_s$ =1nH,  $R_s$ =10  $,C_s = 100 \, \text{fF}$  ,周波数=1GHzという条件で $P_s$ を計算すると  $,P_s = V^2/Zs = 0.1 \, V^2$ となる(V:電圧 ,Zs=(( $L_s$ + $R_s$ )// $C_s$ )) .周波数が 3GHzの場合は $P_s$  0.05  $V^2$ で ある . 次に , (2)の配線と基板間の容量が消費する電力 $P_{cox}$ を計算する .  $\mathcal{C}_{ox}$ =1000fFと仮定すると ,1GHzの場合にP<sub>cox</sub> 0.01 V<sup>2</sup> ,3GHzの時にP<sub>cox</sub> 0.02 √<sup>2</sup>となる . この値をP<sub>s</sub>と比較すると , 1GHzの時は 10%程度 , 3GHzの時は 40% となり,想定している 3GHzまでの範囲では無視できない大きさとなる事 がわかる.次に,(3)基板部分の消費する電力 $P_{si}$ のオーダを計算する.  $C_{si}$ =100fF,  $R_{si}$  =1k と仮定すると, 1GHzの時 $P_{si}$  0.001  $V^2$ , 3GHzの時 $P_{si}$ 0.002 V<sup>2</sup>となり, 想定している周波数帯では, 他の部分より 1 桁以下の オーダとなるため無視して良いこととする.

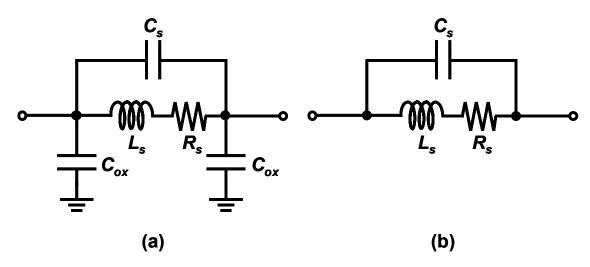

以上の考察より,図 3.1 のモデルは基板部分の等価回路を省略し,図 3.4(a)の様にモデル化できる. さらに,このモデルは, $\mathcal{C}_{ox}$ を $\mathcal{C}_{s}$ へまとめる 事ができるため,図 3.4(b)の様にモデル化する事ができる. 本研究では,図 3.4(b)のモデルを採用し,誘導結合の解析,回路の設計を行ってゆく 事とする.

### 3.3 誘導結合モデル

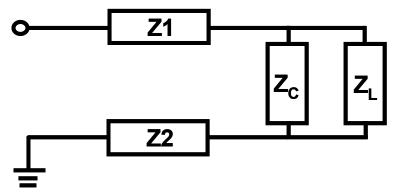

本研究では、図 3.5 に示す誘導結合モデルを採用する.このモデルは、前節で簡単化したインダクタのモデルを送信側受信側で用い,この間を誘導結合で結んだものである.ただし,配線抵抗をインダクタを挟む形で2分する.抵抗を1つでモデル化すると,インダクタと抵抗の順序により送受信波形が異なってしまうためである.

モデル中の結合定数 k は,送信・受信インダクタの物理的形状より決定する.k は送信インダクタが生成した磁束を,受信インダクタが受け取る割合を示す.k の決定方法は,論文[5]で提案されている Current Density Fiber Model (CDFM)を用いる事とする.CDFM はビオサバールの法則を用い,送信インダクタに流れる電流から生成される磁束を計算し,これがどの程度受信インダクタを貫通するかを計算する事で k を求めている.CDFM はチップ間誘導結合通信の研究のために提案された手法であり,エンベディッド・デテクタ([6])を用いた実測により精度を検証している.ただし,周波数解析が行われていない事,インダクタひとつ分のステップでのみズレ(クロストーク)の評価が行われており,小さい値のズレの評価が行われていない事,があり,モデルの評価という意味では,より直接的な測定が必要である.

## 3.4 チップ間誘導結合の測定

提案する誘導結合モデルの正当性を検証するために,実測を行った.測定に用いるチップは0.25μm CMOS テクノロジを用いた.モデルの正当性は,測定時のパラメータを振り,これとモデルが一致する事により評価する.測定により明らかにしたい項目は下記の通りである.

• 測定項目 1 : インダクタの形状依存性

測定項目2:誘導結合の距離依存性

測定項目3: インダクタのズレ依存性

測定項目4:誘導結合の半導体基板依存性(渦電流の効果の評価)

• 測定項目 5 : 電源メッシュによる効果

測定項目 5 は,誘導結合間に電源(グランド)メッシュがあった場合に,誘導結合が減衰する効果を測定する.これは現実のチップが上面全体に電源メッシュを持つため,これらを貫通して通信が可能であるかを調べるものである.ただし,電源メッシュの密度は設計毎に違うため,このテストチップだけの結果であり,参考程度にとどめる事とする.

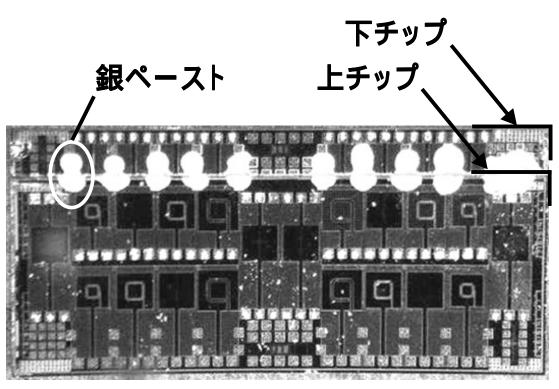

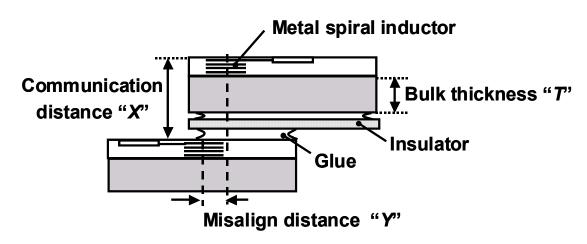

以上の目的の測定を行うために,図3.6に示すチップを作成した.テストチップは2つの同じチップを上下にスタックし,接着材で固定している.断面図を図3.7に示す.インダクタ間の距離はチップを研磨する事により調節する.また,半導体基板依存性については,ソルダボールを用い,チップ間の隙間を作り出す事により,通信距離一定でチップ間の導体の厚みを変化させ評価する2チップ間のグランドは銀ペーストを用い接続した.

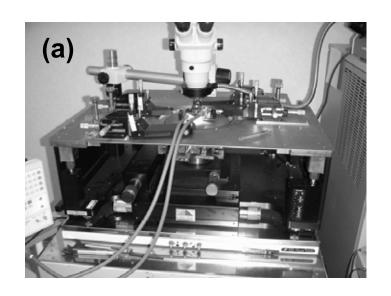

評価を行うインダクタは,測定精度の問題から,通常通信に使うインダクタより大きな自己・相互インダクタンスを持つインダクタを実装した.また,巻き数・直径のパラメータによる差を調べるために,複数のサイズのインダクタを実装した.実装したインダクタのパラメータと自己インダクタンスを表3.1,表3.2に示す.また,先に挙げた測定項目を実測するために,表3.3(測定項目2・3),表3.4(測定項目4)に示す実装を行った.測定項目1・5は各チップ上に異なるサイズのインダクタが搭載されており,全実装で測定可能である.この実装を行ったチップを用い,先に挙げた測定項目1~5を測定した.測定の様子を図3.8に示す.測定器にはAgilent Technologies 社製8753ESネットワークアナライザを用いた.

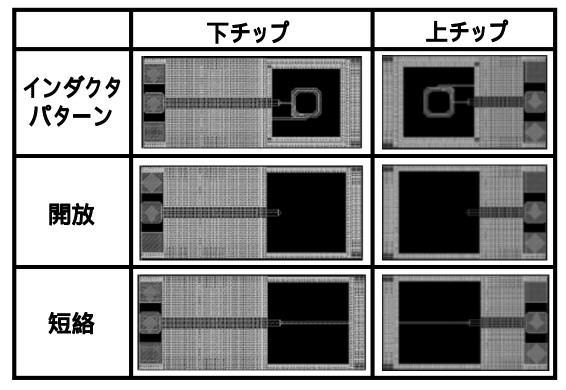

被測定回路であるインダクタのインピーダンスは数 ~数十 である.これに対し,10パッドからインダクタまでの配線が300µm程度あり,この部分のインピーダンスもインダクタと同様な大きさがある.測定の精度を保つために,パッドからインダクタまでの寄生成分を正確に差し引く必要がある.本研究では,パッドからインダクタまでの寄生成分を図3.9の様にモデリングした.通常のインダクタパターンに加え,差し引きのために開放, 短絡のパターンを作成した(表3.5).これらの差し引き用パターンの測定結果をそれぞれる。・2。とし,全体の測定結果を2。,求めたいイン

ダクタのインピーダンスをZ\_とする.開放と短絡,全体の測定結果である式3.1~3.3より,測定したいインダクタのインピーダンスは式3.4の様に求められる.

$$Z_m = Z_1 + (Z_c // Z_L) + Z_2, (3.1)$$

$$Z_{s} = Z_{1} + Z_{2}, (3.2)$$

$$Z_o = Z_1 + Z_c + Z_2, (3.3)$$

$$Z_{L} = \frac{(Z_{m} - Z_{s}) \cdot (Z_{s} - Z_{o})}{Z_{m} - Z_{o}} . \tag{3.4}$$

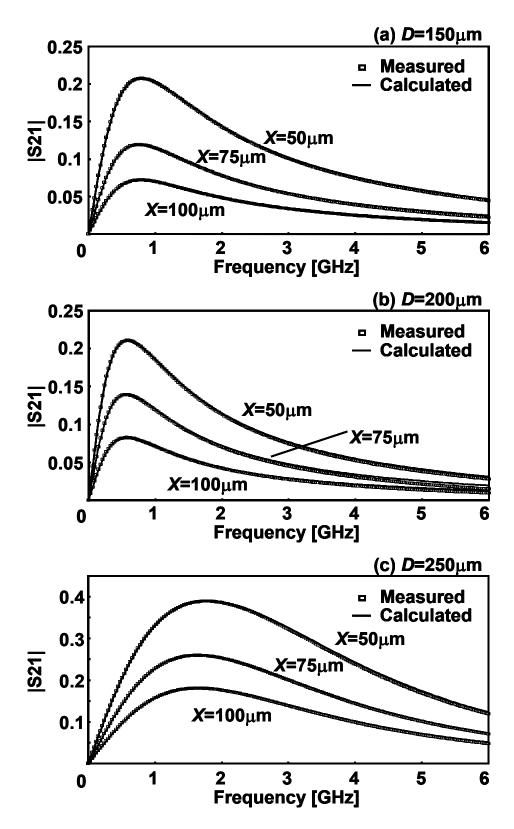

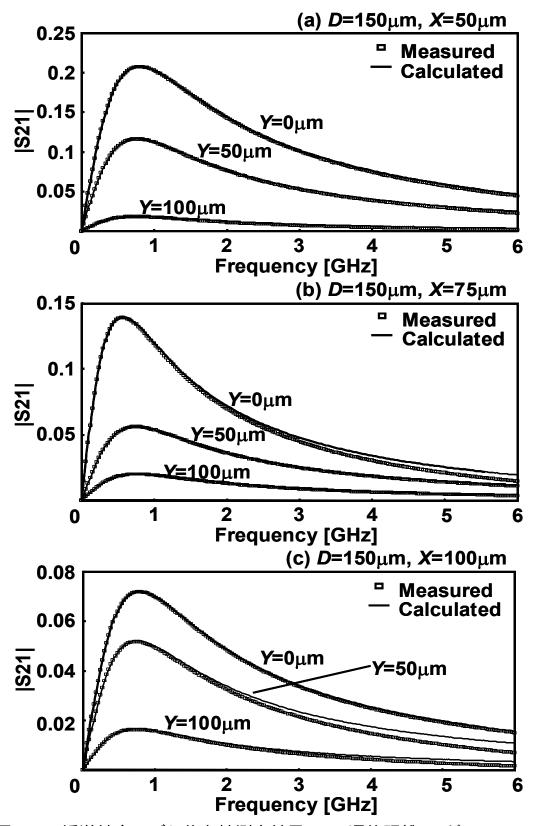

以上の差し引きを行った後の測定結果を図3.10~図3.13に示す.

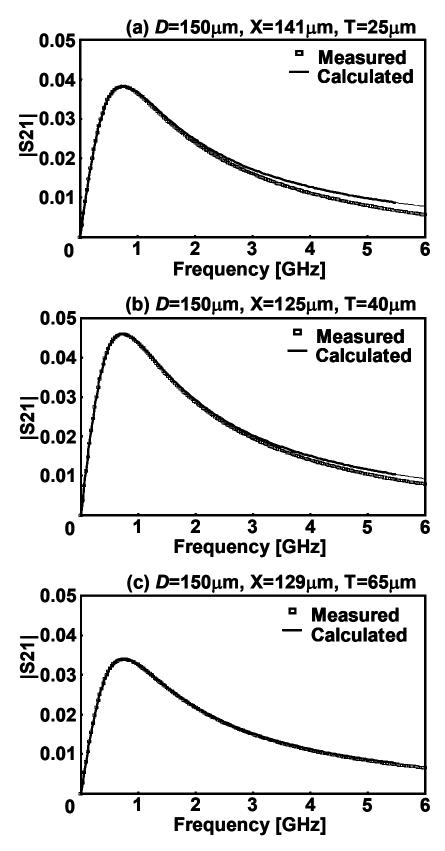

図 3.10 は通信距離とインダクタのパラメータを変化させ、計算値との 比較を行った図である.この図より,どの結果も計算値と良く合致してお り、提案する誘導結合モデルが有効である事を示している、図 3.11 は、 送受信インダクタのズレを測定している.計算に用いている結合定数 kは 論文[5]で提案された手法で計算されている.この結果,計算値と測定値 が良く合致している事から、計算により得られた kが横方向ズレに対して も精度良く見積もられている事がわかった. 図 3.12 は,距離一定で誘導 結合間の材質を変え, 渦電流が通信に影響を与えるか否かを測定した.し かし,距離一定で中間にはさむ材質の厚さを変える実装が困難であり,通 信距離が変わってしまった.このため,図 3.12 では測定した中で,比較 的 Xの変化が少ない結果を示している.この図は  $D = 150 \mu m$  で Tを変化さ せた測定だが, Xが 141μm, 125μm, 129μm と変化している. しかし, いず れの結果も , 測定結果と計算結果が良く一致しているため , 渦電流や基板 による効果は,本研究が前提としている周波数帯では問題とならない事が わかった .図 3.13 はインダクタの下にグランドメッシュを引いた場合と . そうでない場合の結合強度の周波数特性を示したものである.電源メッシ ュは,30μm ピッチで 3μm の配線が格子上に配置されているパターンを用 いた.この結果,500MHz を過ぎてから,結合強度が10%程低下する事が わかった.今回実装した電源メッシュは,実際に用いられている物の一例 であるが,結合度は確実に下がるため,誘導結合間には電源メッシュを引 くべきでない事がわかった.

### 3.5 まとめ

本章では、チップ間誘導結合を用いた無線通信のためのインダクタのモ デルの提案と,そのモデルの測定による検証を行った.インダクタモデル は ,用いる周波数が低い事から ,現在主流のモデルを簡略化した形とした . 誘導結合のモデルは、インダクタのモデルを送信側・受信側に配し、モデ ル中のインダクタ間を結合定数を介して接続する形をとった .結合定数は すでに提案されている CDFM を用いて計算する.このモデルの妥当性を確 かめるために,測定を行った.測定は,チップを実際に積層実装し,チッ プ上のインダクタを直接ネットワークアナライザで S パラメータを計測 した.測定で明らかにする項目は,物理パラメータから求める自己インダ クタンス・結合定数 k・相互インダクタンスの見積もりの正しさ, それか ら、モデルを作成した際に簡単化のために削除した寄生パラメータの影響 の有無である.これらを測定するために,テストチップの際には異なる 径・巻き数を持つインダクタを3種類作成し,積層実装の際に通信距離・ ズレ・距離一定で基板厚の異なる実装を行った,まず,距離を3段階,イ ンダクタの径・巻き数を3種類変えた測定,合計3種類を行った.次に, 距離を3段階変更し、ズレの量を3段階変化させた測定を行った。最後に、 通信距離一定で基板厚を変更した測定を行った.これらの測定の結果,見 積もった S21 とほぼ同じ値を取ることがわかり,提案するモデルと kの計 算手法が,提案する通信手法が対象とする周波数帯で,十分精度を持って いる事がわかった.

図 3.1 シンプルなインダクタモデル.

L<sub>s</sub> 自己インダクタンス

C<sub>s</sub> インダクタの寄生容量

$R_{\rm s}$  インダクタの直列抵抗

C<sub>ox</sub> インダクタ-基板間容量

R<sub>si</sub> 基板抵抗

C<sub>si</sub> 基板容量

図 3.2 型モデル.

図 3.3 two- 型モデル.

- L<sub>s</sub> 自己インダクタンス

- C<sub>s</sub> インダクタの寄生容量

- R<sub>s</sub> インダクタの直列抵抗

- Cox インダクタ-基板間容量

- R<sub>si</sub> 基板抵抗

- C<sub>si</sub> 基板容量

- L<sub>sk</sub> 表皮効果のインダクタンス

- $C_{si}$  表皮効果の直列抵抗

図 3.4 (a)基板の影響を無視したモデル , (b)基板を無視し ,  $\mathcal{C}_{ox}$ を $\mathcal{C}_{s}$ へまとめたモデル .

図 3.5 誘導結合モデル.

図 3.6 積層実装したテストチップ.

図3.7 テストチップの断面図.

図 3.8 (a)測定の様子.(b)プロービング拡大図.

表 3.1 テストチップに実装したインダクタの物理パラメータ.

| Micro-<br>Photograph       |     | D   |     |               |

|----------------------------|-----|-----|-----|---------------|

| Diameter, <i>D</i><br>[μm] | 150 | 200 | 250 | 150, 200, 250 |

| Width, <i>w</i><br>[μm]    | 10  | 10  | 30  | 10, 10, 30    |

| Turns, <i>n</i>            | 8   | 8   | 4   | 8, 8, 4       |

| Ground<br>Mesh             | No  | No  | No  | Yes           |

4-Layer Metal Inductor in 0.25μm CMOS

表 3.2 インダクタの電気的特性.

# Without ground mesh

D=250

# With ground mesh

D=250 Mesh pattern

| Diameter<br>"D"[um] | Width<br>[um] | Turns | Self<br>Inductance<br>[nH] |

|---------------------|---------------|-------|----------------------------|

| 150                 | 10            | 8     | 15                         |

| 200                 | 10            | 8     | 23                         |

| 250                 | 30            | 4     | 8                          |

表 3.3 ズレ・距離依存性測定 (測定項目 2・3).

| <b>Χ [μm]</b>           | 50  | 75 | 100 |

|-------------------------|-----|----|-----|

| T [μm]                  | 40  | 65 | 90  |

| No<br>Miss<br>Align     | X T |    |     |

| 50 μm<br>Miss<br>Align  |     |    |     |

| 100 μm<br>Miss<br>Align |     |    |     |

表 3.4 渦電流の効果測定 (測定項目 4).

| <b>Χ [μm]</b>  | 50    | 75  | 100 |

|----------------|-------|-----|-----|

| T = 25<br>[μm] | X T L | 絶縁体 |     |

| T = 40<br>[μm] |       |     |     |

| T =60<br>[μm]  |       |     |     |

図3.9 被測定回路と寄生成分のモデル化.

表 3.5 差し引き用パターン.

図 3.10 誘導結合(S21)の距離依存性測定結果.(a)インダクタの直径(D)が 150μm の時,(b) D=200μm,(c) D=250μm.

図 3.11 誘導結合のズレ依存性測定結果 . (a)通信距離( $\chi$ )が 50 $\mu$ m の時 , (b)  $\chi$ =75 $\mu$ m の時 , (c)  $\chi$ =100 $\mu$ m の時 .

図 3.12 誘導結合における渦電流の効果.

図 3.13 グランドメッシュによる効果.

## 参考文献

- [1] C.P.Yue and S.S.Wong, "Physical Modeling of Spiral Inductors on Silicon," *IEEE Transactions on Electron Devices*, vol. 47, no.3, pp.560-568, Mar. 2000.

- [2] A.M.Niknejad and R.G.Meyer, "Analysis, Design, and Optimization of Spiral Inductors and Transformaers for Si RF IC s," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 10, pp.1470-1481, Oct. 1998.

- [3] J.R.Long and M.A.Copeland, "The Modeling, Characterization, and Design of Monolithic Inductors for Silicon RF Iss," *IEEE Journal of Solid-State Circuits*, vol.32, no.3, pp.357-369, Mar. 1997.

- [4] I.C.H.Lai, M.Fujishima, "A New On-Chip Substrate-Coupled Inductor Model Implemented With Scalable Expressions," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 11, pp.2491-2499, Nov. 2006.

- [5] N.Miura, D.Mizoguchi, T.Sakurai, and T.Kuroda, "Analysis and Design of Inductive Coupling and Transceiver Circuit for Inductive Inter-chip Wireless Superconnect," *IEEE Journal of Solid State Circuits*, vol. 40, no. 4, pp.829-837, Apr. 2005.

- [6] M. Nagata, J. Nagai, T. Morie, and A. Iwata, "Measurements and Analysis of Substrate Noise Waveform in Mixed Signal IC Environment," *IEEE Transaction on CAD*, vol. 19, no. 6. pp.671-678, Jun. 2000.

# 第4章 送受信回路

## 4.1 緒言

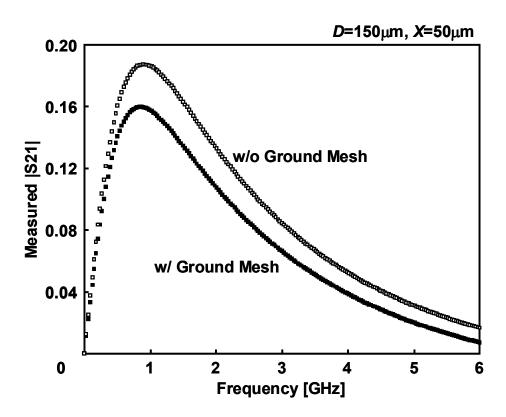

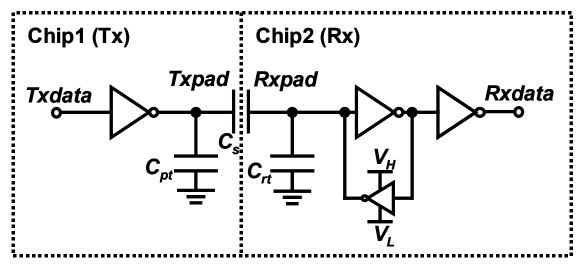

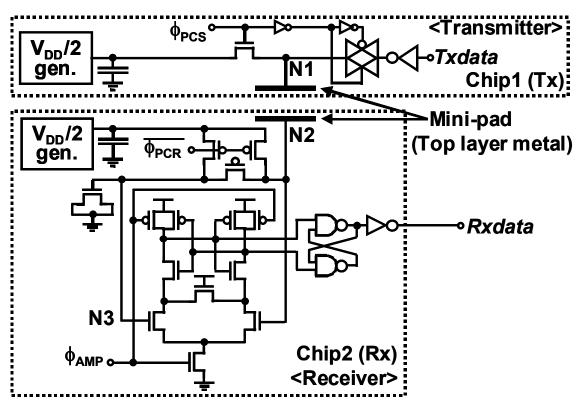

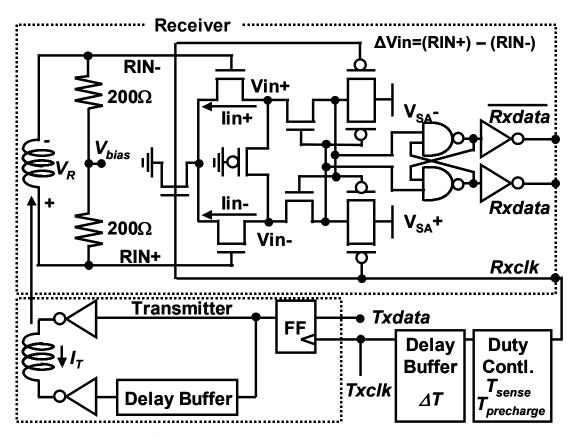

2章で送受信方式を提案したが,本章ではこの方式を実現する送受信回 路を提案する . チップ間通信の送受信回路として , 容量結合方式を採用す る論文[1][2]がそれぞれ図 4.1, 図 4.2 の様な回路を提案している. どち らの方式も,送信器はインバータで直接送信用電極にデジタルデータを印 加している.受信器は図 4.1 では , 1 段目のインバータにフィードバック をかけ、インバータの入力が閾値近辺に保持されるよう調整している.こ れにより、インバータのゲインは最大となる、このインバータに受信電圧 が印加されると,入力波形に応じて反転出力がなされ,後段のインバータ でフルスイングのデジタルデータを出力する.この方式では,非同期デジ タル信号を直接送受信できるという利点がある.ただし,インバータの入 力を常に閾値近傍にバイアスしているため,常時電流が流れ,消費電力面 で不利である、図4.2の受信器は、受信回路にラッチ付きの差動型センス アンプを採用している . 容量結合はシングルエンド信号であるため . 入力 の片側をバイアスに接続している.入力電圧を,クロックの High の期間 にサンプリングし, Low の期間はアンプのプリチャージとデータの保持を 行う.本方式はクロックの High の期間のみテール電流源に電流が流れ, 消費電力の面で有利である.ただし,送受信のクロックの位相が揃ってい る必要がある.

これらの送受信回路,特に受信回路は,シングルエンドの受信信号を想定しており,差動入力の誘導結合方式に適用できない.本章では,誘導結合方式に適した送受信回路を提案する.また,ばらつきを考慮した回路内の各パラメータの決め方について議論する.

## 4.2 送受信回路

2 章で述べたNRZ方式送受信器を実現するために,送信器は入力信号の 遷移に合わせて送信電流を流す必要があり,受信器はインダクタ端に生じ る差動の受信電圧をデジタルデータに変換・保持する必要がある.この動 作を実現するために,図4.3に示す回路を提案する.送信器は遅延素子付 きのH-Bridgeで実現した.この回路により,遅延素子の遅延時間分だけ, インダクタに送信電流が流れる.受信器は,ラッチ付き差動アンプを採用した.受信器は図4.2に近い構成を取っているが,インダクタの両端をそれぞれ差動対に接続する事により,より効率のよい受信器となっている.また,インダクタの両端をバイアスする事により,差動アンプのゲインを制御する事が可能となる.また,差動アンプのゲインは,受信クロックのHighの期間の調整でも行える.図4.3には,この調整を行う,受信クロックのデューティコントローラも示している.また,クロックのHighの期間は,受信電圧 V<sub>R</sub>の振幅が存在する期間にタイミングが合っている必要があるため,受信クロックの位相制御回路も図4.3に示している.

本送受信器の動作を,3章で提案した誘導結合モデルを用いてシミュレーションを行った結果(図 4.3)を例に説明する.送受信インダクタのサイズ,通信距離はそれぞれ100 $\mu$ mを想定し,送受信器は0.35 $\mu$ mCMOSを用いた.基本的な動作は次の通りである.まず,デジタルの送信波形が送信器に入力される.送信器は,遅延素子の時間だけ送信電流/ $\tau$ を流し,インダクタには3角波形状の電流が印加される.この電流の1階微分形状の電圧 $V_R$ が受信インダクタに生じる. $V_R$ は差動アンプで増幅され,この電圧がアンプ上部に接続されたラッチの閾値を超えると,ラッチに値が取り込まれる.値の取り込みはクロックがHighの期間のみ行われる.クロックがLowになると,プリチャージ期間となり,差動対のソース側のノードはLowとなり,ラッチは値の保持期間となる.

## 4.3 受信器の感度調整

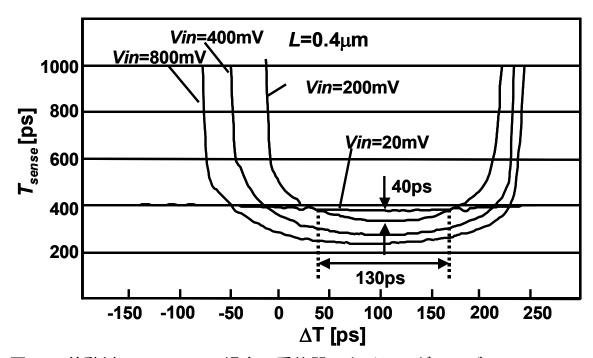

受信器は感度を高めるほど,微小な信号を受信しやすくなるが,ノイズや製造ばらつきに弱くなる.受信器には,ノイズ耐性と,製造ばらつきへの耐性が求められ,これは差動対のトランジスタのチャネル長を大きくする事で実現できる.チャネル長の決定は,ばらつきの大きさとタイミングマージンに依存する.本節では,表4.1にまとめる仕様を満たすよう,チャネル長の決定を行う事とする.

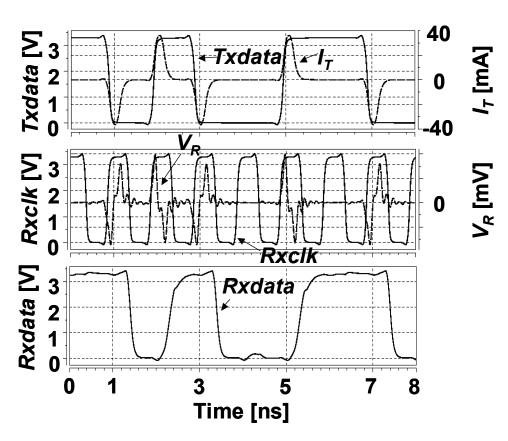

図 4.4 で基本的な送受信の動作を示したが ,ここでは感度調整について論じるために , 受信器の内部 J ードの動作について述べる . 図 4.5 に図 4.3 に示す受信機の内部 J ードの動作を示す . インダクタ端の各 J ードの電位を RIN+ , RIN-とし , この電位差を Vin=(RIN+)-(RIN-)と定義する . また , NAND を 2 つ利用したラッチの入力 J ードをそれぞれ Vsa+ , Vsa-と

する .まず , Vin が受信信号に応じて変化し ,この信号に応じた電流 /in+ , /in-が差動対に流れる . この電流に応じた微小な電位差が ノード Vin+ , Vin-に生じ ,これらのノードの先のクロス接続されたインバータで電位差を広げる . このインバータの出力が Vsa+ , Vsa-であり , ラッチに入力される . 受信信号がある場合には Vsa+ , Vsa-のどちらかがラッチの閾値を越え , 保持しているデータが反転する .

受信データが来ない場合は、クロックの High の期間は Vin が変化しないか、ノイズ等で微小に変化する.差動対は理想的には電気的に完全に対称であり、入力の変化が無ければ /in+、/in-は等しいはずであるが、製造ばらつきやノイズの影響で必ずどちらかに振れてしまう.図 4.5 中で受信データがない場合、Vsa+、Vsa-は同じ電位を保っている必要があるが、Rxc/kが Low になる前には差が生じている.製造ばらつきやノイズによるVsa+、Vsa-の遷移を、ラッチが取り込まない様に受信器のパラメータを調整する必要がある.この調整を、センスアンプのゲイン調整とクロックのHigh の期間の調整の両方で行う.差動アンプのゲイン調整は差動対のチャネル長を変える事で行う.

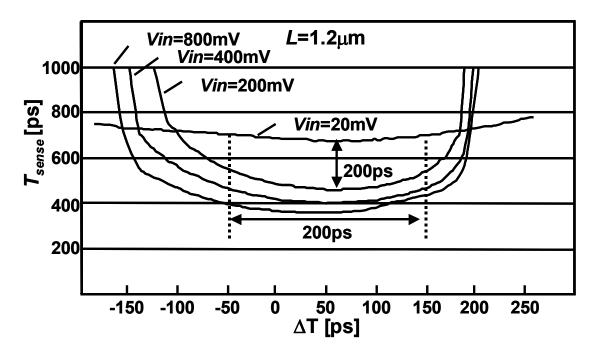

受信器の感度調整を行う際に,製造ばらつきとして,差動対の NMOS のチャネル幅に±5%差をつけ評価を行う.まず,0.35μm プロセスで許される最小のチャネル長 *L*=0.4μm で差動対を作成した場合のタイミングマージンをシミュレーションで確認した.図 4.6 にこの結果を示す.縦軸に受信クロックの High の期間,横軸に受信クロックの位相を取っている.この図は,ラッチが正常にデータの受信・保持が出来るか否かを示し,線のより上が正常受信できる領域である.この図では,受信電圧 *Vin* を0.02mV ~ 0.2mV まで振った結果である.表 4.1 にまとめた通り,ノイズを10mV 以下,信号を 100mV 以上としたため,ノイズ最大 *Vin* は 20mV,信号の *Vin*は 200mV 以上となる.この図で, *Vin*=20mV の線はノイズを示しており,この線を越えるとノイズを受信してしまうという意味である.*Vin*が 200mV 以上で *Vin*が 20mV 以下が,データを正常に受信・保持で

である. この結果では,正常受信できる領域(タイミングマージン)が,最大で40psの幅となっている.表4.1より,クロックジッタは±100psと仮定しいているため,タイミングマージンは200ps必要である.

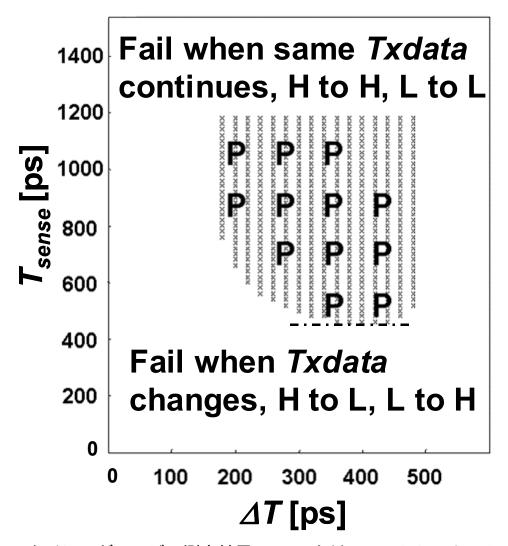

差動対のサイズを調整し、タイミングマージンが 200ps となる領域を調査したところ、 $L=1.2\mu m$  であった.この場合のタイミングマージンの図を図 4.7 に示す.この図より、タイミングマージン 200ps を確保できる領域が存在し、この場合、 Tのタイミングマージンも 100ps 以上確保できて

いる事がわかる.また, *Tsense* は 500ps 程度に設定すれば良い事もわかる.デューティ 50%のクロックを用いる場合には,周期が 1ns となり,目標の 1GHz を達成できた.

### 4.4 まとめ

本章では,誘導結合を用いたチップ間無線通信のための送受信器を提案 した.送信器は遅延素子つきの H-Bridge, 受信機はラッチ付きセンスア ンプで実装した.また,受信機クロックは,位相とデューティの制御を行 う.この制御により受信機の感度調整を行い,所望のタイミングマージン を得る.タイミングマージンとは,クロックの揺らぎに対する耐性の事を 指し,本通信手法ではクロックの位相とデューティの変化に対し正常受信 可能な領域の広さを指す . タイミングマージン決定の制約条件として , ビ ットレート,受信信号・ノイズの値の閾値,クロックジッタ,ばらつきが 考えられる.本章ではこれらの値を, 0.35μm CMOS テクノロジを用いた場 合を仮定して決定した.この制約条件下で,タイミングマージンを満たす トランジスタのパラメータの決定を行った.まず,プロセスルールの許す 最小のチャネル長でセンスアンプを構成した場合のタイミングマージン を求めた.この場合,受信感度が高いが,高いために同一データが連続し た場合(受信データが無い場合)に ,ノイズの影響でデータの保持に失敗す る領域が広く,正常受信可能な領域はクロック位相の範囲で 130ps となっ た.これは, 想定していたクロックジッタ±100ps の変動があると, 誤動 作する事を意味する.次に,センスアンプのトランジスタサイズを大きく してゆき, ばらつきに強くしていった.この結果, チャネル長が1.2μmの 時に十分なタイミングマージンが得られ,位相・デューティ幅,共に200ps のマージンを持つ事がわかった.以上のタイミングマージンの見積もりに より,提案している通信手法は,製造ばらつき・ジッタ等の不確定要素が あっても,通信を確立できる事がわかった.

図 4.1 容量結合方式の送受信器回路例 1.

図 4.2 容量結合方式の送受信器回路例 2.

図 4.3 提案する送受信回路.

図 4.4 提案する送受信回路のシミュレーション波形.

表 4.1 受信感度決定の条件.

| データレート  | 1Gbps   |

|---------|---------|

| 受信信号レベル | 100mV以上 |

| ノイズレベル  | 10mV以下  |

| 製造ばらつき  | ± 5%以下  |

| クロックジッタ | 100ps以下 |

図 4.5 受信器の内部ノードの動作.

図 4.6 差動対の L=0.4 $\mu$ m の場合の受信器のタイミングマージン .

図 4.7 差動対の  $L=1.2 \mu m$  の場合の受信器のタイミングマージン.

- [1] R.J.Drost, R.D.Hopkins and I.E.Sutherland, "Proximity Communication," *IEEE Proceedings of Custom Integrated Circuits Conference*, pp.469-472, Sept. 2003.

- [2] K.Kanda, D.D.Antono, K.Ishida, H.Kawaguchi, T.Kuroda and T.Sakurai, "A 1.27Gb/s/ch 3mW/pin Wireless Superconnect (WSC) Interface Scheme, "IEEE International Solid-State Circuit Conference Digest of Technical Papers, pp.186-187, Feb. 2003.

# 第5章 実験

## 5.1 緒言

本章までに,チップ間の誘導結合のモデル,送受信器のパラメータ決定について述べた.本章では,テストチップを試作し,実際にチップ間で通信を行い,提案しているシステム,モデル,パラメータ決定方法が正しい事を検証する.

# 5.2 評価方法

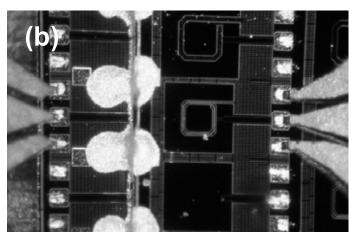

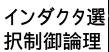

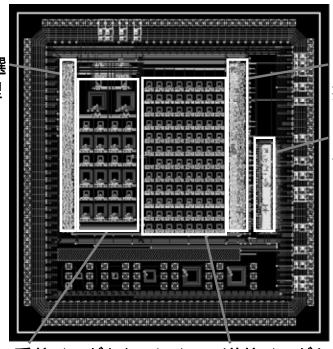

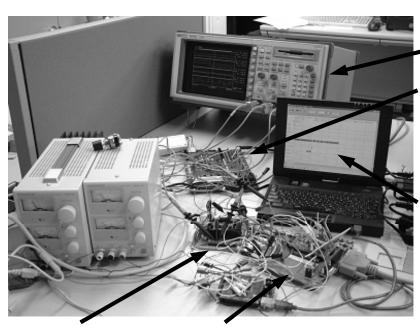

テストチップの作成には,前章までの議論で用いてきた 3 層メタル 0.35μm CMOS プロセスを用いた.同一チップ上に送受信器を実装し,上にスタックするチップの位置を調整し,上下の送受信インダクタの位置が合うようにする.ここで,位置合わせの精度が問題となる.実装環境の問題から,上下チップは数十~数百μm のズレが生じることが予想された.そこで,送信器・受信器を異なるピッチでアレイ状に配置し,スタック時に180 度回転する事とした.アレイ中の任意のインダクタを選択可能にする事で,位置の最も合っているインダクタ対を選択し,通信を行う事が可能である.スタック時には,上チップを180 度回転させるため,外部とのインタフェースはチップの4辺のうち,1辺からのみとした.通信距離を削減するために,上チップを研磨した.研磨の状況により通信距離が変化し,場合によっては距離が遠くなり結合定数が低下する可能性があるため,複数のインダクタサイズを実装した.設計したチップのレイアウトを図 5.1 に,実装したインダクタを表 5.1 にまとめる.また,実際にスタックした状態の写真を図 5.2 に示す.

テストチップには,アレイ状に配置した送受信器の他に,テストに必要となる擬似ランダムデータ発生器(31bit LSFR),送受信器セレクタ,位相シフタ,クロックデューティ変更器,32bit データ用 FIFO を搭載している.この構成により,可能となるテストは下記の3つである.

実験 1. 外部から直接テストデータ印加,外部での受信データの観測本実験は,データ・クロック共に外部から供給する.内部のクロックデューティ変更器により, *Tsense* の High 期間を持つクロック

を作り出す.これにより,十分遅いビットレートで通信を行う事が出来る.

#### 実験2.タイミングマージン測定

内部にある 31bit LFSR とクロックジェネレータを用い,送受信を行い,送受信終了後,エラーがあったか否かの確認をする.このテストを,クロックの位相・デューティを変化させて行い,タイミングマージンのマップを作成する.

以上のテスト結果を次節で述べる.

## 5.3 実験結果

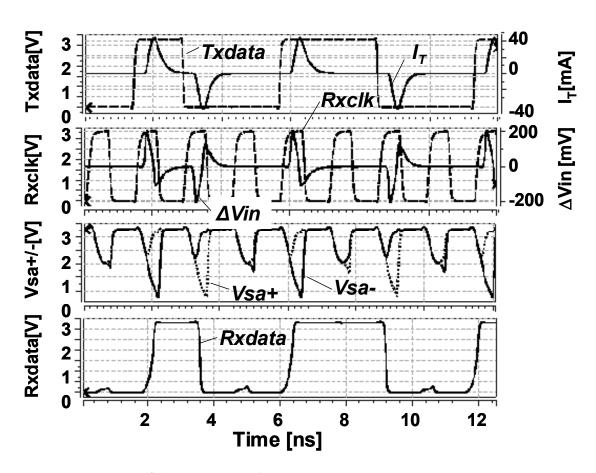

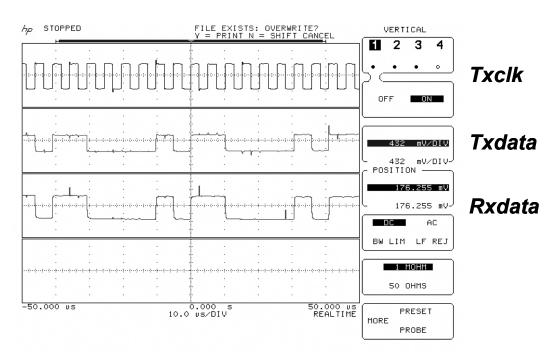

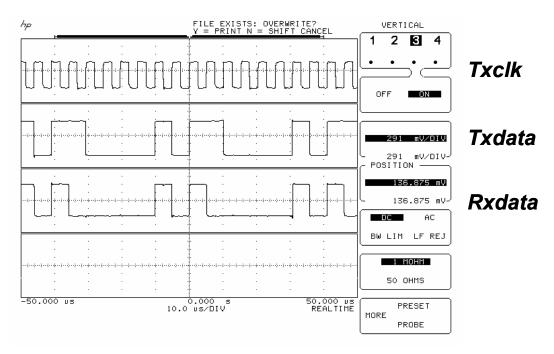

まず,実験1の外部からデータ・クロックを直接与える実験について述べる.本実験の測定環境を図5.3に示す.本テストは,実チップで通信が可能である事,クロックの位相とデューティの制御機能が正しく動作する事を確認するテストである.クロックの位相・デューティを振った結果,正常にデータを送受信できる事を確認した.図5.4に送受信波形を示す.通信距離は300μm,受信インダクタのサイズは300μm,クロック周波数は20kHzである.設計値より十分遅いクロックでデータの保持が出来ているため,クロックデューティの制御が成功していると考えられる.また,クロックデューティを広げた結果,値の保持が出来なくなる現象も観測できた(図5.5).以上より,提案する無線通信システムが正常に動作する事が確認できた.

次に内部のクロック制御機能を使い,タイミングマージンを測定した.この結果を図 5.6 に示す.図中のPマークが実測でビットエラーレート (Bit Error Rate, BER) 10<sup>-9</sup>を達成した場所である.図中のxマークはシミュレーションで通信が出来た場所である.実測でのタイミング・デューティの変更ステップは 70psであり,かなり荒いが,ほぼシミュレーション結果と同じ領域で通信が出来ている.また,図中の,通信可能領域の下に引いてある破線部分が最も高速に通信が出来た場所で,*Tsense*=450ps,*Tprecharge*=340psであり,1.27Gbpsの通信が達成できた事になる.この際の電力は送信側 43mW,受信側 2.5mWであった.

## 5.4 まとめ

本章では、提案している誘導結合方式のチップ間通信手法を実測により検証した検証用のチップを 3 層金属配線  $0.35 \mu m$  CMOS プロセスで作成し、実際に積層実装を行った、積層チップ間の通信を試み、 $300 \mu m$  の距離で通信に成功した。また、タイミングマージンの測定を行い、シミュレーション結果と一致した。以上の結果より、提案するシステム、モデルが正しい事が検証できた。また、目標性能を超える 1.27 Gbps を達成できた。この際の電力は、受信側が 2.5 m W、送信側が 43 m W であり、送信側が支配的であった。

インダクタ選 択制御論理

クロック制御 論理

受信インダクタアレイ 送信イ

送信インダクタアレイ

図 5.1 テストチップレイアウト図.

表 5.1 実装したインダクタのパラメータ.

| <b>D</b> [μm] | n  | <b>w</b> [μm] | s [μm] | L [nH] |

|---------------|----|---------------|--------|--------|

| 100           | 8  | 5             | 1      | 7      |

| 200           | 10 | 5             | 1      | 35     |

| 300           | 12 | 5             | 1      | 90     |

図 5.2 スタック実装を行ったテストチップの写真.

・オシロスコープ テストデータ・クロック 生成用FPGAボード

ロジックアナライザ

テストチップ マイコンボード(送受信制御用)

図 5.3 測定環境.

図 5.4 正常動作している送受信波形.

図 5.5 デューティ制御を行い,データの保持が出来なくなった波形.

図 5.6 タイミングマージン測定結果 .x マークは SPICE シミュレーション で通信可能であった点 , P は実測で通信できた点 .

第6章 磁界一定のスケーリング則

## 6.1 緒言

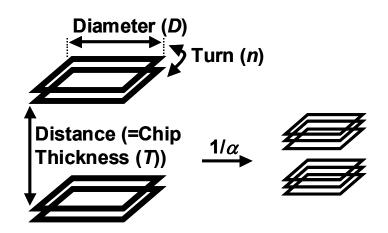

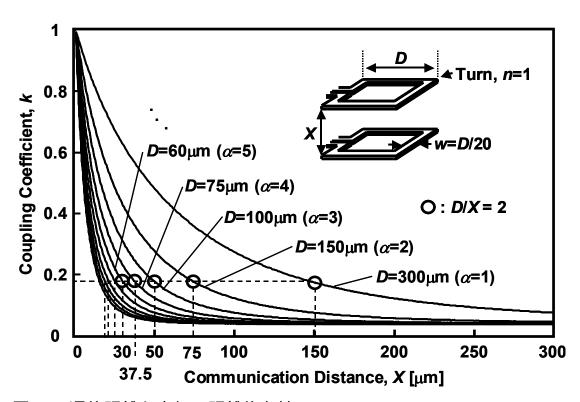

本研究では、シングルチャネルのチップ間無線を提案し、1Gbps/ch の性能を達成した([1]).本方式は、チャネルを2次元に配列(図6.1)して、全体のバンド幅を向上できる利点を持つ.チャネルを並べると、クロストークが問題となるが、これは送信タイミングを近接するチャネルからずらす技術や、最適な送信電力を選択する技術により緩和する事が出来る.クロストークを緩和する事により、論文[2]では、送受信器をアレイ状に195チャネル配置し、195Gbpsを達成している.この際のインダクタ径は48μmで、垂直方向の通信距離は15μmであった.さらに、論文[3]では1024チャネルを用いて1Tbpsの通信に成功している.この際のインダクタ径は30μm、通信距離は15μmであった.今後、小面積でトータルバンド幅を向上するために、単位面積あたりのチャネル数を増加させる必要がある.このためには、インダクタの直径の縮小が必要となる.

インダクタの直径を縮小すると,一般的に,結合度が低下し,通信の電力効率が低下する.直径の縮小による効率の低下は,インダクタの巻き数を増やす事と,通信距離を小さくする事でカバーできる.これは,インダクタ間の磁界が一定に保たれるからである.本章では,トランジスタで電界一定の法則([4])を用いたスケーリング則が成り立つように,誘導結合方式データ通信でも磁界一定の法則を用いて,今後も本通信方式がスケーリングして行く事を議論する.

# 6.2誘導結合の式の解析

簡単化のため,スケーリングの前提条件として,送信・受信インダクタは同じパラメータを持つと仮定する $(L_{R}=L_{T}=L)$ .すると,式(2.4)より,受信電圧 $V_{R}$ は下記の様になる.

$$V_R = L \frac{dI_T}{dt} \,. \tag{6.1}$$

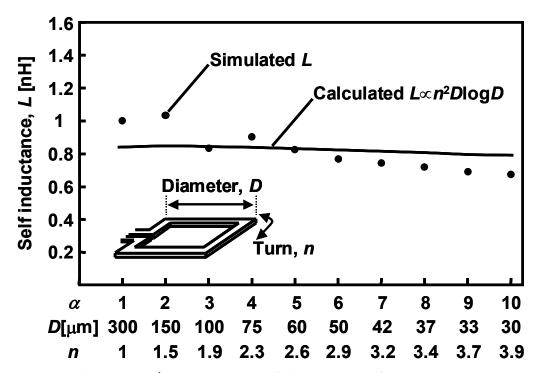

Lは物理的特性から,巻き数nの 2 乗に比例し,また,インダクタの直径をDとすると, $D\log D$ に比例する.本論文では,簡単化のため,この式を最小二乗法を用いて指数形式に近似する.近似を行う範囲は,本論文中で用いている最大のインダクタサイズである  $300(\mu m)$  から、最小の値 1 とする.この範囲では, $D\log D$ は $D^{1,2}$ と近似される.このため,Lは次式の様に与えられる.

$$L = L_0 n^2 D^{1/2}. {(6.2)}$$

$L_{\rho}$ は単位面積をもつ 1 回巻きインダクタの自己インダクタンスを表し,nは巻数,Dは直径を表す.式(6.2)の正当性は,6.4章でシミュレーションと実測により実証する. $d/_{\tau}/dt$ は,トランジスタを用いた場合,

$$\frac{dI_T}{dt} = \frac{I_D}{t_{pd}} , \qquad (6.3)$$

と表される. $I_p$ はドレイン電流で, $t_{pd}$ は伝播遅延時間である.以上より, $V_a$ は下記の様に表される.

$$V_R = kL_0 n^2 D^{1.2} \frac{I_D}{t_{nd}} . {(6.4)}$$

通信はパルスベースであるため,信号の周波数大域が広がり,通信路のパスバンドの広帯域化が必要となる.式(6.4)は周波数成分の議論を含んでいない.周波数成分を含んだ議論を行うために,誘導結合のモデル(図3.5)の伝達関数を求めると,下式の様になる.

$$\frac{V_{R}}{V_{T}} = \frac{1}{1 + j\omega C_{R}R_{R}} \times j\omega k \sqrt{L_{T}L_{R}}

\times \frac{1}{R_{out}(1 - \omega^{2}L_{T}C_{T}) + R_{T} + j\omega(C_{T}R_{T}R_{out} + L_{T})}.$$

(6.5)

# 6.3 スケーリング則の前提条件

チャネルを縮小する際に,BERを一定とするために,V<sub>o</sub>が一定である事を

制約条件として与える. V<sub>R</sub>はBERを決めるEyeの開口の,電圧成分の特性を 決めるからである.開口の時間方向はジッタに依存するため,ここでは議 論しない.ここで,スケーリングファクタ を定義する. はプロセスの 各パラメータの寸法の変化を示す,無次元のスケーリングファクタである. スケーリングの議論は,インダクタサイズ,データレート,通信距離を1/ する事を条件として進める.送受信回路に用いるトランジスタは従来の スケーリング則([4])に則る事とする.これらの条件を表6.1にまとめる.

## 6.4 磁界一定のスケーリング則

スケーリングの前提条件を満たす様,インダクタの各パラメータのスケーリングファクタを決定する.最も大きい制約は $V_R$ 一定である. $V_R$ を一定とするためには,式(6.4)中の各項を一定とする必要がある.式(6.1)より, $I_D$ は1/ に比例し,回路の遅延時間 $I_D$ は1/ に比例するため,式(6.4)中の最後の項 $I_D$ / $I_D$ は一定となる.また, $I_D$ 0は定義より定数であるため, $I_R$ 2を一定値とするためには残りの項, $I_D$ 2が定数となればよい.この2項を定数とするために $I_D$ 2のスケーリングファクタを決定する.

k はインダクタの物理的な形状により決定する.2 つのインダクタのパラメータが全て に比例して変化した場合(図 6.2),2 つのインダクタを貫く磁束は一定となり,kは一定となる.このため,インダクタサイズを 1/ した場合,通信距離 Xを 1/ にすると,Kを一定にできる.Xを削減する事は,チップの裏面を研磨する事に等しい.現在のチップ厚は  $300\mu$ m 前後だが,メモリの積層チップでは  $50\mu$ m 程度が実用化されている.さらに,研究レベルでは基板厚を  $1.7\mu$ m まで薄くしてもトランジスタの性能は劣化せずノイズ特性がよくなったという報告([5])もあるため,基板の研磨は実現可能であると考えられる.

次に,  $n^2 D^{-2}$ の項を一定とする必要がある. Dは 1/ に比例すると仮定したため,  $n^{-1}$ が <sup>0.6</sup>に比例すればよい. 巻数は, 配線総数を増やせは容易に増やす事が可能である. 配線総数はプロセスの進歩に伴い増加するため, <sup>0.6</sup>に比例して増加させる事は可能であると考えられる.

以上, $V_R$ を一定とするためのインダクタパラメータのスケーリング則を提案した.このスケーリング則を元に,単位面積当りのバンド幅( $1/t^D$ )とビット当りのエネルギー( $1_T t_{pd}/V$ )を見積ると,バンド幅が  $^3$ に比例し,

電力が 1/3に比例することがわかった .また ,インダクタの周波数特性 , 伝達関数の特性は ,後に述べるシミュレーションにより , に比例して改善される事がわかった . 以上のスケーリングの結果を表 6.2 にまとめる .

# 6.5 スケーリング則の検証

前章で $V_R$ を一定とするスケーリング則を提案した.この際に, $L_o$ は定数であり, $I_o$ / $t_{po}$ は従来のスケーリング則に則っているため,一定と結論づける事ができた.しかし,kと $r^2D^{-2}$ が一定になる事については検証が必要である.そこで,本節では,kと $r^2D^{-2}$ の項がそれぞれ一定となる事をシミュレーションと実測で検証する.

k は物理パラメータの比で決まるため,送信インダクタと受信インダクタ,通信距離がすべて比例縮小すると一定となるはずである.この仮定を確かめるために,インダクタシミュレータ([6])を用いて,1 回巻きのインダクタを D, X, w を変えてシミュレーションを行った.図 6.3 に結果を示す.横軸が通信距離を表し,縦軸が kを表す.w は D/20 と仮定した.この図で,D/X が 2 となる場所を各世代で比べると,k が一定(約 1.8)となっている事がわかる.この結果より,D, X, W が比例縮小すると,k は一定となることがわかる.

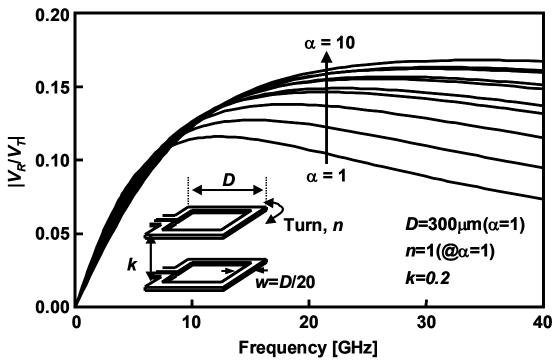

次に, $\hat{R}D^{1.2}$ が一定となることをシミュレータにで検証した.この結果を図 6.4 に示す.解析対象としたのは =1 の時にD=300 $\mu$ m,n=1 のパラメータを持つインダクタで, を 1 から 10 まで変化させ, $n^2D^{1.2}$ が一定となることを確かめた.図 6.5 の計算値は, =1 の値で正規化している.この結果より,計算式とシミュレーション値は良く一致し,スケーリングにかかわらず, $\hat{R}D^{1.2}$ は,ほぼ一定の値を取ることがわかった.

以上,シミュレーションにより提案スケーリング則の正しさを述べたが,次に実測値が,提案する見積りに一致することを述べる.実測したインダクタは,過去に発表された論文([1-3][7])で用いられたものである.この結果を表 6.3 にまとめる.それぞれ,パラメータは に比例していないが,Lと $r^2$  $D^{-2}$ の値を 0.35 $\mu$ mの時の値で正規化している.この結果,本稿で提案する見積もり手法と,実測が,それぞれ良く一致している事がわかる.

## 6.6 周波数特性のスケーリング則

提案したスケーリング則は周波数特性を考慮していないが,スケーリングにより式(6.5)の周波数特性が改善してゆく事を,シミュレーションと 実測により示す.

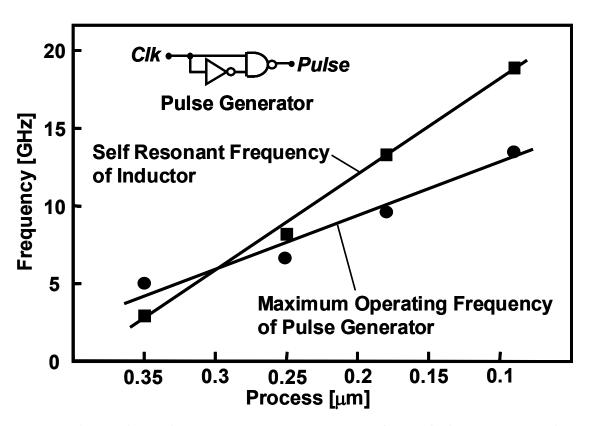

まず,自己インダクタンスの周波数特性を調べる.本研究が前提としている誘導方式通信はパルスベースの通信であるため,パルスの中心周波数が自己共振周波数に近いとビットエラーレートが悪化する.このため,共振周波数は十分高い必要がある.図6.5は,各世代のインダクタの共振周波数と,論文[2]で述べられているパルスジェネレータの最大周波数をプロットしたものである.インダクタのパラメータは図6.4と同じ物を用いた.この図より,世代が進むほど,自己共振周波数は,送信パルスの周波数より十分高くなっていくことがわかる.この結果より,自己共振周波数はスケーリング時に問題とならないと考えられる.

次に,式(6.5)の周波数特性を が1から10までスケーリングした場合について図6.6にシミュレーション結果を示す.この図作成時に用いたインダクタのパラメータは図6.4と同じである.図3.5の $C_{7}$ ,  $C_{8}$ を求める際に,メタルとGND間は40aF/ $\mu$ m²,  $R_{8}$ ,  $R_{7}$ を求める際にはシート抵抗0.08 /sq.を用いた.この図より,スケーリングが進むほど,パスバンドが広がっている事が見て取れる.これは,インダクタの小型化により寄生容量が低下したためだと考えられる.この結果より,スケーリングは,伝達特性の改善に寄与することがわかった.

# 6.7 まとめ

本章では,通信チャネルを2次元に配置した場合に,総バンド幅が製造プロセスの進歩に対してスケーラビリティを持つことを議論した.議論の前提として,受信電圧を一定とする事とした.これは,ビットエラーレート一定を意味する.この条件下で,無次元の比例定数スケーリングファクターを導入し,インダクタサイズ・トランジスタサイズがプロセスの進歩に比例して1/ にスケーリングする条件で議論を進めた.以上の条件を,受信電圧を決定する式に適用すると,通信距離を1/ ,巻き数を 0.6して行く事により,受信電圧を一定としつつインダクタサイズを1/ にスケー

リングできる事がわかった.さらに,これらのスケーリングファクタを用いて,バンド幅,消費電力の見積もりを行った.この結果,バンド幅は ³に比例して増加し,ビット当りの消費電力は ³に反比例することがわかった.さらに,このスケーリングが正しい事を示すため,シミュレーションと実測で理論値と比較を行った.この結果,理論値はシミュレーション,実測のどちらともよい一致を見せた.また,インダクタと伝達関数のスケーリング時の周波数特性の解析を行った.この結果,自己インダクタンスは今後のスケーリングで問題とならない事がわかり,伝達関数はスケーリングにより特性が改善することがわかった.以上より,誘導結合方式チップ間無線通信は,プロセスの進歩の恩恵を受け,今後もバンド幅の向上と低電力化を進める事ができると結論付けられる.

図 6.1 総バンド幅向上のための 2 次元チャネルアレイ.

# 表 6.1 スケーリングの前提条件.

| Transistor Size      | [x]                         | 1/α |

|----------------------|-----------------------------|-----|

| Power Supply Voltage | [ <i>V</i> ]                | 1/α |

| Current              | [ <i>I<sub>T</sub></i> ]    | 1/α |

| Circuit Delay Time   | $[t_{ ho d}] \sim [CVII_T]$ | 1/α |

| Coil Diameter        | [ <i>D</i> ] ~[1/x]         | 1/α |

図 6.2 インダクタのスケーリング.

# 表 6.2 スケーリング則.

| Coil Turn Number (Layer #) [n]                        | α0.6             |

|-------------------------------------------------------|------------------|

| Chip Thickness [7]                                    | 1/α              |

| Self Inductance [L]~[n²DlogD]                         | 1                |

| Magnetic Coupling Coefficient [k]                     | 1                |

| Receive Signal $[V_R] \sim [kn^2D\log D(I_H t_{pd})]$ | 1                |

| Crosstalk $[V_{RS}/V_{RN}]$                           | 1                |

| Data Rate / Channel [1/t]                             | α                |

| Channel Number / Area [1/D²]                          | $\alpha^2$       |

| Self Resonance Frequency [Hz]                         | α                |

| Pass Band [Hz]                                        | α                |

| Aggregated Data Rate / Area [1/tD²]                   | $\alpha^3$       |

| Energy / Bit $[I_T t_{pd}/V]$                         | 1/α <sup>3</sup> |

図 6.3 通信距離と直径の距離依存性.

図 6.4 自己インダクタンスの近時式による見積もりとシミュレーション結果の比較.

表 6.3 実測したインダクタのスケーリングパラメータ.

| Chip Micro-<br>Photograph                     |      | [2]  | [3]  | [7]  |

|-----------------------------------------------|------|------|------|------|

| Process[μm]                                   | 0.35 | 0.25 | 0.18 | 0.09 |

| <i>D</i> [μm]                                 | 300  | 48   | 30   | 20   |

| n                                             | 2    | 4    | 4    | 4    |

| L(Measured)[nH]                               | 2.98 | 1.76 | 0.88 | 0.45 |

| L (Normalized)                                | 1    | 0.59 | 0.29 | 0.15 |

| <i>n</i> 2 <i>D</i> log <i>D</i> (Normalized) | 1    | 0.43 | 0.23 | 0.14 |

図 6.5 自己共振周波数(シミュレーション)とパルス生成器の最大周波数の比較.

図6.6 誘導結合の伝達関数のスケーリングによる効果.

# 参考文献

- [1] D. Mizoguchi, Y. B. Yusof, N. Miura, T. Sakurai, and T. Kuroda, "A 1.2Gb/s/pin Wireless Superconnect based on Inductive Inter-chip Signaling (IIS)," 2004 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 142-143.

- [2] N. Miura, D. Mizoguchi, M. Inoue, H. Tsuji, T. Sakurai, and T. Kuroda, "A 195Gb/s 1.2W 3D-Stacked Inductive Inter-Chip Wireless Superconnect with Transmit Power Control Scheme," 2005 *IEEE International Solid-State Circuits Conference*, *Digest of Technical Papers*, pp. 264-265. Feb. 2005.

- [3] N. Miura, D. Mizoguchi, M. Inoue, K. Niitsu, Y. Nakagawa, M. Tago, M. Fukaishi, T. Sakurai, and T. Kuroda, "A 1Tb/s 3W Inductive-Coupling Transceiver for Inter-Chip Clock and Data Link," *IEEE International Solid-State Circuits Conference*, *Digest of Technical Papers*, pp.424-425, Feb. 2006.

- [4] D. Dennard, F. H. Gaensslen, H. Yu, V. L. Rideout, E. Bassous, and A. R. Leblanc., "Design of Ion-Implanted MOSFET s with Very Small Physical Dimensions," *IEEE Journal of Solid-State Circuits*, vol. Sc-9, No. 5, Oct. 1975, pp.256-267.

- [5] T. Ohguro, N. Sato, M. Matsuo, K. Kojima, H.S. Momose, K. Ishimaru and H. Ishiuchi, "Ultra-thin chip with permalloy film for high performance MS/RF CMOS," *Symposium on VLSI Technology Digest of Technical Papers*, pp.220-221, June 2004.

- [6] A.M.Niknejad and R.G.Meyer, "Analysis, Design, and Optimization of Spiral Inductors and Transformers for Si RF IC s," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 10, Oct. 1998.

- [7] N. Miura, H. Ishikuro, T. Sakurai, and T. Kuroda, "A 0.14pJ/b Inductive-Coupling Inter-Chip Data Transceiver with Digitally-Controlled Precise Pulse Shaping," *IEEE International Solid-State Circuits Conference*, Dig. Tech. Papers, pp.264-265, Feb. 2007.

# 第7章 結論

#### 7.1 はじめに

近年,インターネットが普及し,さらに,携帯電話に代表される移動体 通信や無線 LAN 等のワイヤレス機器の普及により ,いつでもどこでも大量 の情報を得る事が可能なユビキタスコンピューティングが現実の物にな りつつある. 今後は UWB 技術が実用化され, ユビキタスコンピューティン グはさらに身近になると考えられる .ユビキタスコンピューティングに欠 かせない物が小型携帯端末であるが、これには、高機能・小型・低消費電 力・低コストが望まれる.個人が持つ端末は,携帯電話を例に取ると,力 メラ機能,ブラウザ機能,電子メール送受信機能,動画・ワンセグメント TV 録画・視聴機能など,非常に多彩な機能を持つ.これらの機能を実現 するためには、マイクロプロセッサが欠かせないが、すべての処理をマイ クロプロセッサ1個で実現するためには,動作クロックを上げる必要があ る.消費電力は動作クロックの2乗に比例して増加するため,バッテリ駆 動の小型携帯端末では ,単純にクロックを増加して処理を行う事はできな い.このため,一般的には,各機能に特化した専用回路を搭載し,電力効 率を良くし,処理速度を保ったまま低電力を達成する.小型携帯端末は, プロセッサチップと専用処理用チップ,データ保持用のメモリチップを組 み合わせてシステムを構成する事が一般的である.これらのチップは,従 来ボード上に実装されていたが,近年の微細化技術の進歩により,1Chip に納めることが可能となってきた.一方で,1Chipに全機能を搭載すると, チップ面積が増大し,歩留まりが低下し,コストが高くなるといった欠点 があった.これに対し,各チップを1パッケージに納める,SiPが提案さ れ,製品化されている.SiP は異なるプロセスを用いて製造されるチップ を容易に接続できる利点や,良品を選別した後に実装可能である利点があ る.一方で,チップ間の接続については,物理的接続を後から施す必要が あり、速度、数を増やす事が難しい、SiP内接続で最も多く用いられてい るのがワイヤボンディングである.ワイヤボンディングは従来技術の延長 で容易に接続が可能である反面、チップの端のみの接続で数を増やせず、 また寄生のインダクタンスが付き信号の速度を早く出来ないといった欠 点を持つ.一方,近年,マイクロバンプや貫通電極といった,3 次元にチ ップを積層実装した SiP に特化したチップ間接続が提案されている .ただ し,これらは微細な物理的加工が必要となり,歩留まりが上がらず,コス トが高い.

以上の様なSiPについての現状を鑑み、本研究では積層実装されたチッ

プ間の通信を高速に行う事を目的とした.この目的を達成するために,本研究では誘導結合を用いたチップ間無線通信方式を提案した.この通信方式は,積層実装されたチップ上に通信用のインダクタを形成し,上下チップのインダクタ間に形成される誘導結合を用いてデータの通信を行うものである.この様な形態の通信は,本研究以外に例を見ないため,必要となる技術すべてをゼロから構築する必要がある.具体的には,積層チップ間の誘導結合についてと,送受信回路についての技術を提案しなければならない.これらの技術について研究を行い,2章以降で述べた.

以下に本研究で得られた結論を各章ごとに分けて記述し,最後に総括を する.

# 7.2 誘導結合を用いたチップ間通信手法の提案 (2章)

積層実装チップ間を無線で通信を行うために誘導結合を用いた方式を提案した.チップ上にインダクタを形成し,上下チップ間で位置合わせをしておき,インダクタ間に形成される誘導結合を用いて通信を行う.誘導結合でデータを送受信する場合,受信側の電圧波形は,送信電流の時間微分の波形を得る.ただし,受信信号の大きさは結合定数に比例する.結合定数は,インダクタ径と通信距離を同程度にとると0.1程度となる.このため,送信電力の一割程度が受信側に伝達できる事になるが,通信の効率としては高くない.このため,デジタルの送信データが遷移した時のみ誘導結合を用いてデータを送信する,Non-Return-to-Zero (NRZ)方式を採用し,極力送信電力を削減する事とした.また,本章では容量結合方式との比較を行った.この結果,回路実装面を上側にした積層で,通信距離が離れると誘導結合方式の方が有利である事がわかった.

# 7.3 誘導結合モデル (3章)

回路の検討や通信路の特性を明らかにするために,インダクタのモデルを検討した.インダクタのモデルは十分に研究されており,これを参考にし,目標のデータレート 1Gbps で問題とならない程度に簡単化を行った.これを元に誘導結合のモデルを構築した.次に,モデルが正しい事を実測により検証した.実際にチップをスタックし,ネットワークアナライザを

用いて直接誘導結合を測定した.測定時には,インダクタのパラメータ,通信距離,位置のズレをそれぞれ変化させた.いずれのパラメータを変化させた場合も,測定値とよく合致しており,提案するモデルが正しい事がわかった.さらに,通信距離一定で基板の厚さを変化させた場合の測定も行った.この結果,基板の渦電流が考慮に入っていないモデルによる計算値と測定値がよく合致したため,基板の渦電流の効果は目標のデータレートでは問題とならない事がわかった.また,グランドメッシュを通信路に置いた場合は,1割ほど誘導結合の強度が低下した.これは,メッシュ中に渦電流が生じ電力を消費しているためと思われる.この結果より,電源メッシュは,通信の磁束が通る部分を避けて作成すべきだとの知見が得られた.

# 7.4 送受信回路 (4章)

誘導結合のモデルを構築した後,2章で提案したNRZ方式を実現する送受 信器を提案した.送信器は,遅延素子付きの H-Bridge を採用した.入力 のデジタルデータが遷移すると,遅延素子の遅延時間だけ,送信電流が流 れる、受信器は、ラッチつき作動増幅器を採用した、インダクタに誘導さ れる受信電圧の変化が一定レベルを超えたときのみ,差動増幅器上部に接 続されたラッチが値を取り込む、これらの回路構成により、NRZ 方式でデ ジタルデータを送受信できる事を ,シミュレーションにより確認した .次 に,回路を設計する上で必要となる回路パラメータの決定について検討し た.受信器がノイズを受信せず,データのみを受信出来る様に,差動増幅 器の差動対のトランジスタのサイズを決定する必要があるからである .本 研究では,受信電圧の振幅幅が 20mV 以下をノイズ,200mV 以上を信号と した.また,クロックのジッタが100ps,製造ばらつきが±5%存在すると 仮定した.以上の条件下で,0.35μm CMOS プロセスを想定してタイミング マージンをシミュレーションにより求めた.この結果,差動対のトランジ スタのチャネル長が 1.2μm であると,クロックジッタ,製造ばらつきが存 在しても正常に通信できる事を確認した.

# 7.5 実験 (5章)

送受信回路の検討後,テストチップを作成し,積層実装して通信実験を

行った .テストチップは 3 層配線 0.35μm CMOS プロセスを用いて作成した . チップ内部にクロックの位相制御 ,デューティ比制御回路を搭載しており ,外部からの遅いクロック・データでも送受信が可能となっている . 最初のテストでは ,外部クロック・データを用い ,送受信テストを行った . この結果 ,300μm の距離で通信を確立できた . 次に ,チップ搭載の線形帰還シフトレジスタを用いてビットエラーレートを測定し ,タイミングマージンのマップを作成した . この結果 ,タイミングマージンはシミュレーションで得られた形とほぼ同じ形状となった . また ,最大データレート 1.2Gbpsを達成した . この際の消費電力は ,送信器が 43mW ,受信器が 2.5mW であった .

# 7.6 磁界一定のスケーリング則 (6章)

5章までに1チャネルでの送受信の確立を行ったが,本章では,データ レートを向上するため,チャネルを2次元配列で作成し,総バンド幅の向 上を検討した .プロセス技術の向上によるトランジスタのスケーリング則 がよく知られているが,これを誘導結合方式でも行う事を目的とした.こ こでスケーリングファクタ $\alpha$ を導入した.前提条件として,トランジスタ サイズ,インダクタの直径が  $1/\alpha$ に比例するとした.さらに,スケーリン グの制約条件として,受信電圧が一定となる様,各パラメータを変化させ る事とした、受信電圧を求める式より、受信電圧を一定とするためには、 結合定数と自己インダクタンスが一定となる必要がある事がわかった .こ のため,結合定数を決定するパラメータである通信距離は,インダクタの スケーリングに比例すべきである事が導き出された.また,自己インダク タンスをスケーリング時に一定とするために,巻き数を $\alpha^{0.6}$ に比例して増 やす必要があることが導き出された.以上,通信距離の削減,インダクタ の巻き数のスケーリングファクタを元に,2次元チャネルアレイの密度, 総バンド幅 , 1 ビットあたりの消費電力を見積もると , それぞれlpha , lpha ,  $1/\alpha$ に比例する事がわかった.この結果より,誘導結合方式は,製造プロ セスの微細化の恩恵をうけ,バンド幅を大幅に向上できる事がわかった. 次に,このスケーリング則を検証するために,シミュレーションを行っ た.まず,自己インダクタンスを一定にできるかをシミュレーションで確 認した  $.\,lpha$ が 1 から 10 まで変化した場合に  $.\,$ 巻き数等のパラメータを提案 したスケーリング則に則り変化させ,インダクタ解析ソフトで値を見積も った.この結果,自己インダクタンスは,ほぼ一定となった.次に,結合

定数を一定とするために提案した,通信距離の削減が有効であるかをシミュレーションで確認した.これも,インダクタ解析ソフトを用い, $\alpha$ が 1 から 10 まで変化した時の k の値を見積もった.この結果,インダクタをスケーリングし,同様に距離を削減すると,k が一定となる事が確かめられた.以上に加え,以前に作成し実測したインダクタでも,自己インダクタンスの見積もり方について検証した.この結果,実測結果とも,よく合致する事がわかった.以上,スケーリング則の根拠の確認を行ったが,これらは周波数特性を考慮に入れていない.このため,スケーリングにより自己・相互インダクタンスがどのような影響を受けるかシミュレーションにより調査した.この結果,自己インダクタンスの自己共振周波数はスケーリングに伴い非常に高くなり,送受信のデータレート向上に影響を与えない事がわかった.相互インダクタンスの周波数特性は,伝達関数の周波数特性を解析することとした.この結果スケーリングが進むほど,パスバンドが広がり,より通信に有利となる結果となった.

#### 7.7 総括

本研究では,SiP内の積層チップ間の接続を高速・低電力・低コストで 行うために,誘導結合を用いた通信方式を提案した.この方式を低電力で 実現するために,信号方式として NRZ 方式を採用した.次に,従来は報告 されていなかった積層チップ間の誘導結合のモデル化を行った .提案した モデルは,実測により正当性の検証を行い,本研究が提案している通信方 式では十分な精度を持っている事が確かめられた .通信路のモデル化の後 , 送受信回路の提案を行い、その回路内のパラメータ決定について議論した. この結果, 0.35μmCMOS プロセスを用い, 1Gbps を目標とする場合, ばらつ きやジッタの影響があっても、十分なタイミングマージンを保つ事のでき る回路パラメータが存在する事がわかった.提案したインダクタモデル, 回路,送受信システムを検証するため,0.35μm CMOS プロセスを用いテス トチップを作成した.このチップを実際に積層実装し通信を行ったところ. 最大で 1.2Gbps で通信を確立できた.また,誘導結合モデルと回路モデル から見積もったタイミングマージンと、ほぼ同じマージンを観測する事が でき,モデルの正当性が検証できた.1チャネルでの通信確立後,2次元 にチャネルを配した場合のスケーラビリティについて議論した.この結果, 製造プロセスの微細化に比例したスケーラビリティがある事を示す事が できた.

# 7.8 今後の展望

本研究では、1 チャネルの通信を目的として行ったが、今後は多チャン ネル化した場合の問題点について研究する必要がある .多チャンネル化時 にはチャネル間のクロストークやスキューが問題になると考えられる.6 章で 2 次元配列中のチャネルのクロストークは一定に抑えられる事を議 論したが ,送受信器の設計時には4章で議論した手法に加え ,他チャンネ ルからのクロストークへの耐性も加えて議論する必要が出てくる.スキュ ーについては、チャネル数が増え、チャネル間の距離が大きくなってくる と重大な問題となる、受信器のタイミングマージンの決定時に、クロック ジッタに加え,スキュー分のマージンを加える必要がある可能性がある. もしくは,送信チャネルがデータの転送に用いたクロックを伝送し,ソー スシンクロナス転送を行う事で解決できる可能性がある.この場合,クロ ックの無線伝送技術が必要となる、クロックの伝送は非同期通信となるが、 4章のはじめに紹介している容量結合方式の受信器を応用すると,送受信 可能であると考えられる.また,クロック以外に,電力も無線伝送を行う と, 完全にワイヤレスで SiP を構成可能となる. チップを研磨すると通信 距離が小さくなり ,ある程度大きなインダクタを用いると ,結合定数をほ ぼ1に出来,積層チップ間でトランスを構成可能である.

どんなに優れた技術でも、使われなければ意味がないため、上記の課題に加え、応用製品を見据えた課題も解決しなければならない.まず必要なのはキラーアプリの選定である.積層チップ間を高速・低電力で、通信しなければならないアプリケーションを見つけ、実製品に採用される努力が必要である.2章で挙げたマイクロバンプ技術は、ソニーのプレイステーション・ポータブルで使用された実績がある.これは、画像処理チップション・ポータブルで使用された実績がある.これは、画像処理チップとととよりを、省面積で実装し、さらに高速でデータ転送を行う必要があったからである.この例ではメモリチップ1個と画像処理用のチップ1個を対面で実装している.さらに大容量のメモリが必要となった場合には、からで表している.さらに大容量のメモリとの接続を、産業界にアピールしてゆく事が重要である.実製品に採用されるためには、いくの課題をクリアしなければならない.最も重要な課題が信頼性であり、外部からの影響によりデータ転送に支障を来たさない事と、SiP内の他の機能に影響を与えない事の検証が必要である.まず外部からの、通信チャネル

への影響だが、この影響は小さいと考えられる。外部からの強力な磁界が、1GHz 近傍の周波数で変化し、さらにそれがクロックのエッジに同期して変化するとは考えにくいからである。ただし、同じパッケージ内の、近い回路からの磁界の影響は考慮する必要がある。近年の RF 回路はインダクタを多用しており、この影響の検討については今後の課題である。次に、SiP 内の他の回路への影響だが、これも十分検討する必要がある。RF 回路に用いられているインダクタへの影響や、今後主流になると考えられている磁気抵抗メモリ(Magnetoresistive Random Access Memory。MRAM)への影響を検討すべきであり、これは、今後の課題である。

以上の課題をクリアすれば,誘導結合を用いた積層チップ間通信手法は 広く半導体製品に用いられる事になるだろう.

# 謝辞

本論文を執筆するに当たり,慶應義塾大学総合デザイン工学専攻 黒田 忠広教授には,筆者が慶應義塾大学に在学中の時から終始かわらず懇切丁寧にご指導いただき,本論文の執筆に対しても更なるご指導ならびにご鞭撻を賜りました事に,深く感謝の意を表します.また,本論文の作成に当り,丁寧なご指導とご支援を頂きました慶應義塾大学開放環境科学専攻コンピュータ科学専修 天野英晴教授,総合デザイン工学専攻 中野誠彦准教授,石黒仁揮専任講師に深く感謝の意を表します.

3章の誘導結合の実測に際して,貴重なご意見と闊達な議論を頂きました NEC システムデバイス研究所の深石宗生氏,中川源洋氏に深く感謝の意を表します.また,誘導結合の測定に欠かせないが非常に困難であるチップの研磨と積層実装を行って頂いた,NEC 生産技術研究所の田子雅基氏に深く感謝の意を表します.

## 研究業績

#### 原著論文

- [1] D. Mizoguchi, N. Miura, Y. Yoshida, N. Yamagishi, and T. Kuroda, "Measurement of Inductive Coupling in Wireless Superconnect," Japanese Journal of Applied Physics, vol.45, no.4, pp.3286-3289, 2006.

- [2] D. Mizoguchi, Y. B. Yusof, N. Miura, T. Sakurai, and T. Kuroda, "A 1.2Gbps Non-contact 3D-Stacked Inter-Chip Data Communications Technology," *IEICE Transactions on Electronics*, vol.E89-C, no.3, pp.320-326, 2006.

- [3] D. Mizoguchi, N. Miura, H. Ishikuro and T.Kuroda, "Constant Magnetic Field Scaling in Inductive Coupling Data Link", *IEICE Transactions on Electronics*, Vol.E91-C, no.2, 2008 (accepted for publication).

# 国際会議

- [1] D. Mizoguchi, Y. B. Yusof, N. Miura, T. Sakurai, and T. Kuroda, "A 1.2Gb/s/pin Wireless Superconnect based on Inductive Inter-chip Signaling (IIS)" 2004 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 142-143, (ISSCC 2004, San Francisco, USA, 2004).

- [2] D. Mizoguchi, N. Miura, M. Inoue, and T. Kuroda, "Design of Transceiver Circuits for NRZ Signaling in Inductive Inter-chip Wireless Superconnect," 2005 International Conference on Integrated Circuit Design and Technology, Digest of Technical Papers, pp. 59-62, May 2005, (ICICDT 2005, Austin, USA, 2005).

- [3] D. Mizoguchi, N. Miura, Y. Yoshida, N. Yamagishi, and T. Kuroda, "Measurement of Inductive Coupling in Wireless Superconnect,"

- 2005 International Conference on Solid State Devices and Materials, Extended Abstracts, pp. 670-671, (SSDM 2005, Kobe, Japan, 2005).

- [4] D. Mizoguchi, N. Miura, H. Ishikuro and T.Kuroda, "Constant Magnetic Field Scaling in Inductive-Coupling Data Link," 2006 International Conference on Solid State Devices and Materials, Extended Abstracts, pp. 606-607, (SSDM 2006, Yokohama, Japan, 2006).

#### 国内学会・研究会

[1] D. Mizoguchi, Y. Yusof, N. Miura, T. Sakurai, and T. Kuroda, "A 1.2Gb/s/pin Wireless Superconnect Based on Inductive Inter-Chip Signaling," 平成16年5月集積回路研究会,電子情報通信学会技報,vol.104, no.67, pp. 31-36, (電子情報通信学会,金沢,2004).

#### その他

#### 特許出願

- [1] 黒田忠広, 櫻井貴康, 溝口大介, ユスミラズ・ビンティ・ユスフ, 三浦典之, 「電子回路」 特開 2005-228981

- [2] 黒田忠広, 櫻井貴康, 溝口大介, ユスミラズ・ビンティ・ユスフ, 三浦典之, 「電子回路」特開 2005-348264

- [3] 黒田忠広, 溝口大介, 三浦典之, 「電子回路」 特開 2006-50354

- [4] 黒田忠広, 溝口大介, 三浦典之, 「電子回路」 特開 2006-66454

- [5] 黒田忠広, 溝口大介, 三浦典之, 「電子回路」 特開 2006-105630

- [6] 黒田忠広, 溝口大介, 三浦典之, 「電子回路」 特開 2006-173415

- [7] 黒田忠広, 溝口大介, 三浦典之, 「電子回路」 特開 2006-173986